PRICE \$4.95

(May be applied towards the purchase of the Model 10)

# THE MODEL 10 TRIGGER EXPANDER

**(For Use With the Model 100A Logic Analyzer)**

## INCLUDES:

- Using the Model 10 to Expand the Model 100A

- How to use the Controls

- Understanding Circuit Operation

- Assembly & Test of the Model 10 Kit

- Troubleshooting

- Applications of the Model 100A/Model 10

**PARATRONICS, INC.**

**CAUTION**

REFER TO THE MODEL 100A MANUAL BEFORE

CONNECTING THE BLANKING OUTPUT OF THE

ANALYZER TO YOUR SCOPE. OTHERWISE THE

SCOPE's Z-AXIS INPUT CIRCUIT MAY BE

DAMAGED.

Copyright © 1977 by Paratronics, Inc. All rights reserved--no part of this manual

may be reproduced in any form, including translations, without the specific written

permission of the publisher, Paratronics, Inc., 800 Charcot Ave., San Jose, CA 95131.

## TABLE OF CONTENTS

| <u>SECTION</u> |                                                             | <u>PAGE</u> |

|----------------|-------------------------------------------------------------|-------------|

| 1.0            | INTRODUCTION .....                                          | 1-1         |

| 2.0            | MODEL 10 SPECIFICATIONS .....                               | 2-1         |

| 3.0            | WHAT THE CONTROLS DO .....                                  | 3-1         |

| 4.0            | HOW IT WORKS .....                                          | 4-1         |

| 5.0            | GETTING THE KIT TOGETHER .....                              | 5-1         |

| 6.0            | CHECKING IT OUT .....                                       | 6-1         |

| 7.0            | WHAT IF IT DOESN'T WORK RIGHT? .....                        | 7-1         |

| 8.0            | OPERATING THE MODEL 10 BY ITSELF AS A WORD RECOGNIZER ..... | 8-1         |

| 9.0            | OPERATING THE MODEL 10 WITH OTHER ANALYZERS .....           | 9-1         |

| 10.0           | S-100 BUS APPLICATION EXAMPLE .....                         | 10-1        |

| 11.0           | THE WARRANTY & RETURN SHIPPING INFORMATION .....            | 11-1        |

## APPENDIX - MICROCOMPUTER APPLICATIONS

|      |                                                   |        |

|------|---------------------------------------------------|--------|

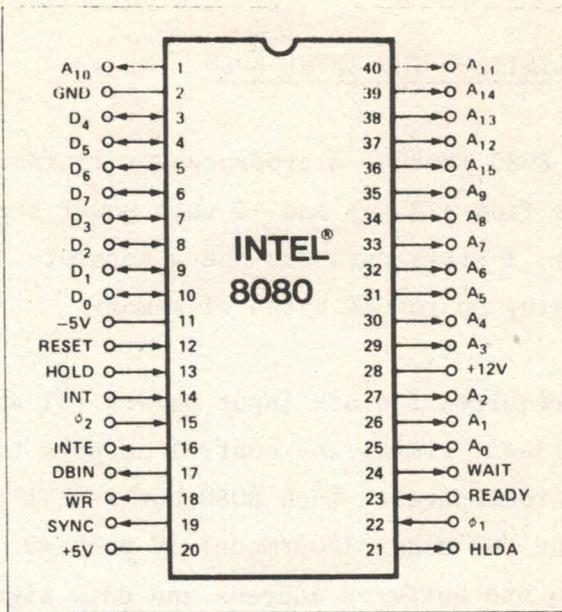

| A.1  | LOGIC ANALYSIS OF THE INTEL 8080 .....            | A.1-1  |

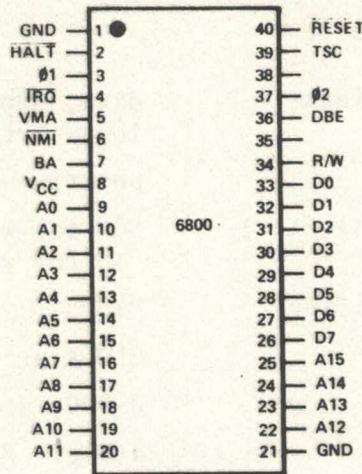

| A.2  | LOGIC ANALYSIS OF THE MOTOROLA 6800 .....         | A.2-1  |

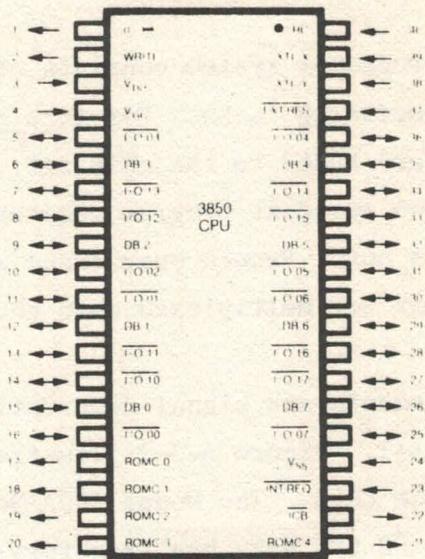

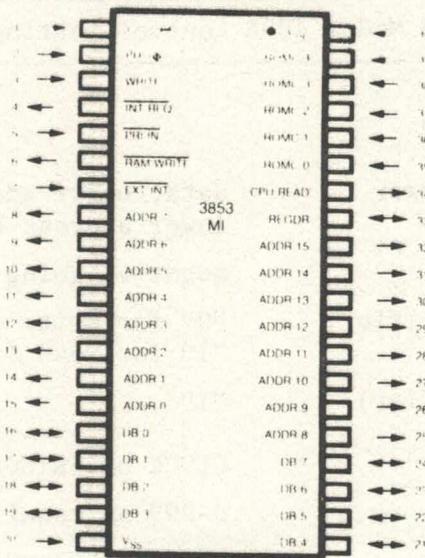

| A.3  | LOGIC ANALYSIS OF THE FAIRCHILD F8 .....          | A.3-1  |

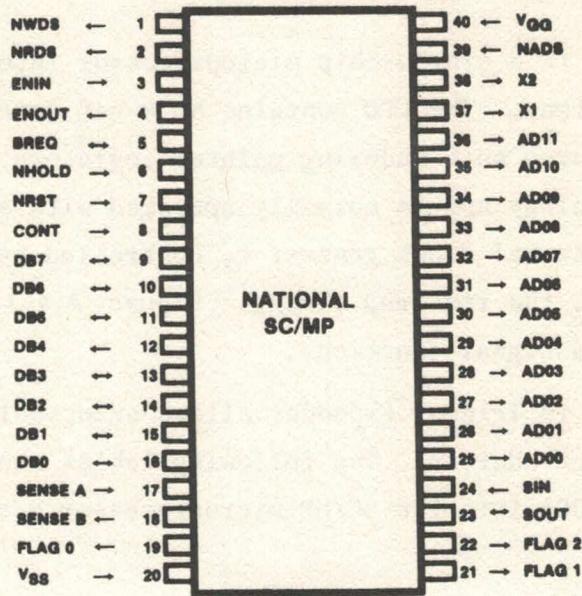

| A.4  | LOGIC ANALYSIS OF THE NATIONAL SC/MP .....        | A.4-1  |

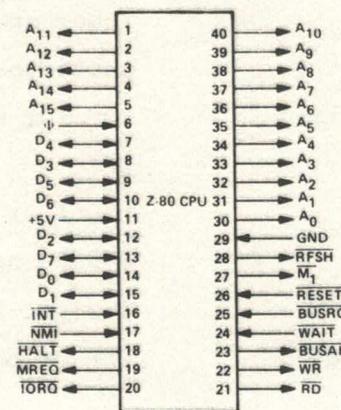

| A.5  | LOGIC ANALYSIS OF THE ZILOG Z-80 .....            | A.5-1  |

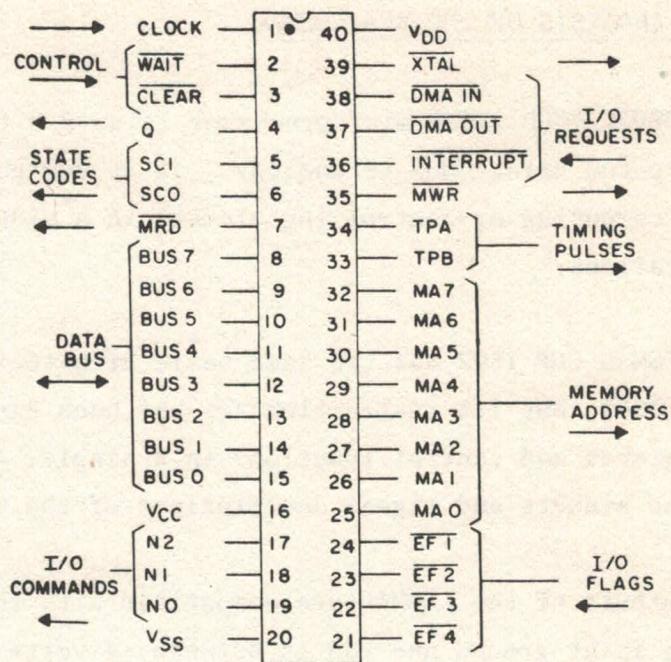

| A.6  | LOGIC ANALYSIS OF THE RCA COSMAC .....            | A.6-1  |

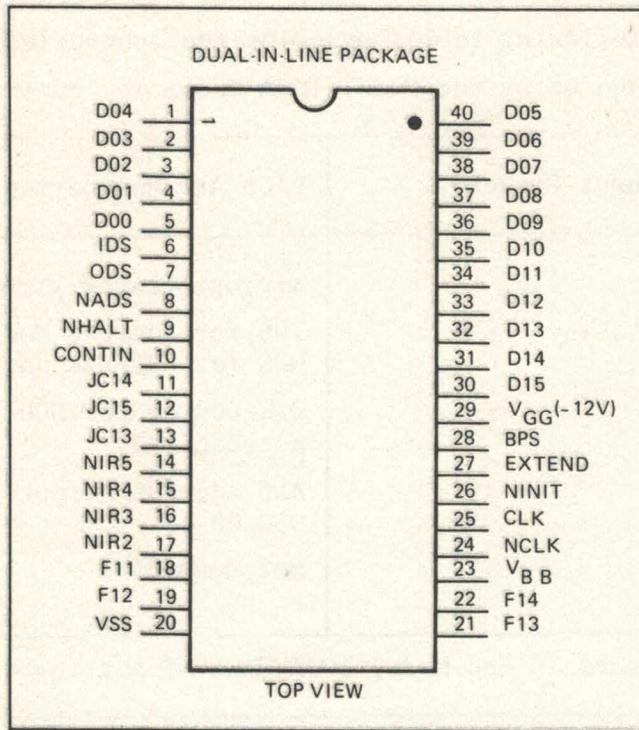

| A.7  | LOGIC ANALYSIS OF THE PACE SYSTEM .....           | A.7-1  |

| A.8  | LOGIC ANALYSIS OF BIT-SLICE MICROPROCESSORS ..... | A.8-1  |

| A.9  | FIELD SERVICE APPLICATIONS .....                  | A.9-1  |

| A.10 | PRODUCTION TESTING APPLICATIONS .....             | A.10-1 |

There is no doubt that the introduction of the microprocessor several years ago has revolutionized the electronics industry. More and more companies, educational institutions and individuals are using microprocessor-based systems.

When the first low-cost logic state analyzer (the Model 100A) was introduced through a cover article in the February 1977 issue of Popular Electronics, the resulting large response from a wide variety of customers provided us with a great deal of insight about how deeply the microprocessor had penetrated into both industrial and nonindustrial areas. Customers who acquired the Model 100A Logic Analyzer for use with their microprocessor systems included large and small computer corporations, power and tire companies, the inmates of a state penitentiary, wineries, amusement parks, all manner of schools and hobbyists, and even a chewing gum manufacturer!

Why has the Model 100A been so popular? The answer is related to the low cost of today's basic microprocessor systems. For example, a "starter" system consisting of a CPU board, a small amount of memory, a chassis and a power supply can be purchased for just a few hundred dollars. But the related supporting test equipment--such as logic analyzers--has historically required an investment of several thousand dollars or approximately ten times the cost of the simple microprocessor system. For many companies, schools and individuals just getting into the design and use of microcomputers, this type of investment for supporting equipment was difficult, if not impossible, to justify. Yet the inherent complexity of a microprocessor system requires sophisticated logic analysis techniques for development, maintenance, and training: the old scope-and-ohmmeter method are just not enough. Thus, the introduction of the Model 100A came at a time when the microcomputer user needed a logic analyzer at a price compatible with the cost of his system. And since the Model 100A has many of the features of units costing much more, it is enjoying widespread use.

The Model 100A's low price was made possible through the use of efficient design and packaging techniques as well as by eliminating some of the more complicated and less frequently used "bells and whistles" of more expensive analyzers.

However, as microcomputing systems increase in complexity, the user may find that the basic analysis capabilities of the Model 100A are not adequate. For example, with the Model 100A you can trigger from and view the activity on the 8-bit data bus. But let's say as you view this bus, you find that it's necessary to capture and display only STORE instructions occurring after a particular 16-bit address. The Model 100A alone can't satisfy this requirement. And that's where the Model 10 Trigger Expander comes in. Without affecting any of the basic features of the Model 100A, the Model 10 adds the following capabilities: 16-bit address bus triggering, qualifiers for monitoring selected data, digital delay for paging through long programs, and the viewing of the events on the address bus as well as the data bus without having to move the input probes.

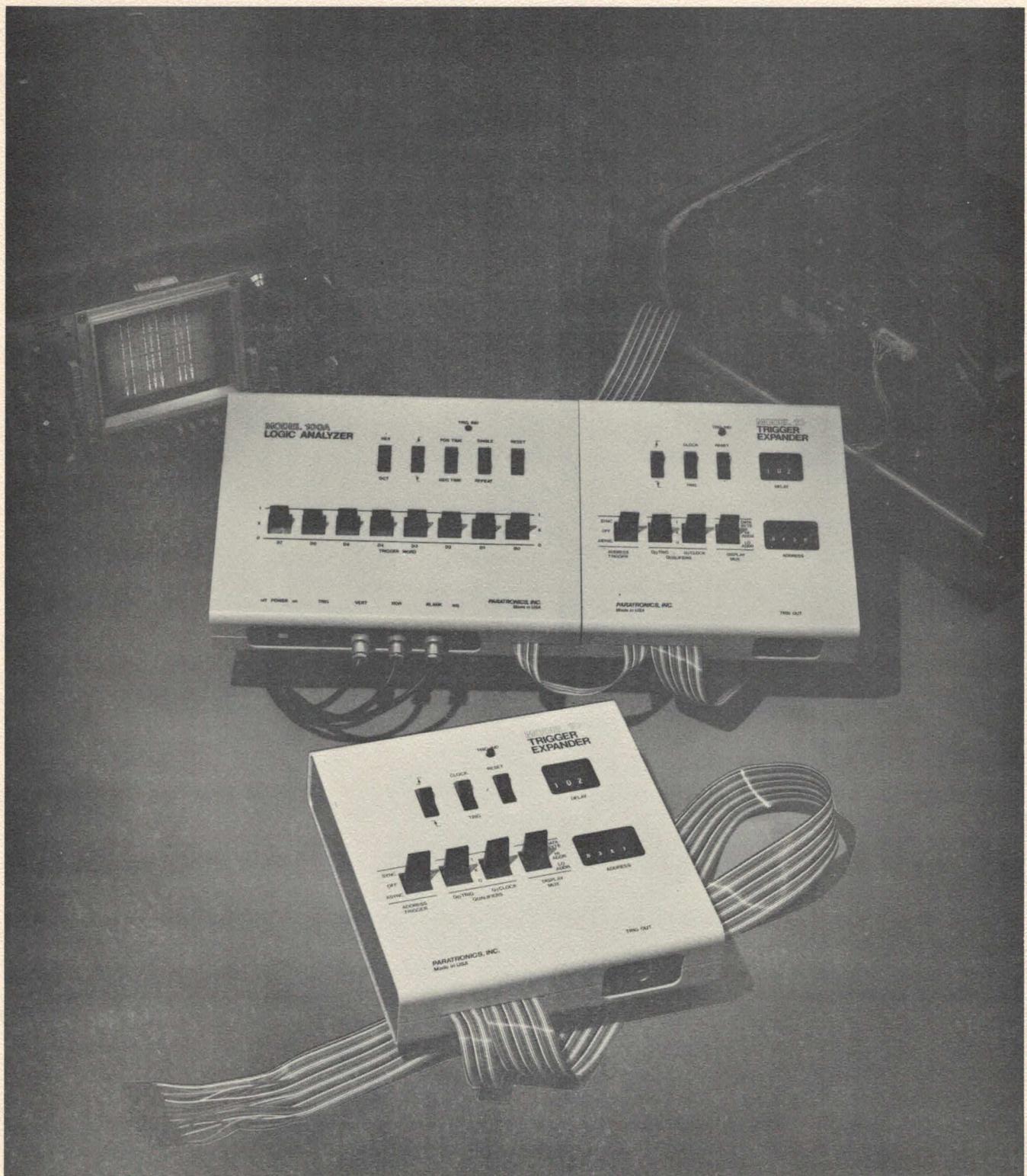

All Model 100A Logic Analyzers in the field can readily be upgraded with the Model 10. As shown in the photo at the front of the manual, the two units mechanically interlock to form a single, integrated package.

By way of summary, Table 1-1 compares the features of the Model 100A alone, the Model 100A and the Model 10, and the Hewlett-Packard HP-1607 Logic Analyzer.

The Model 10 is another member of P.I.'s growing family of high-quality, cost-effective instruments and systems. P.I. will continue to develop these affordable products, each providing the high performance and advanced features demanded by the microprocessor user.

If you have any questions or comments about our products, we'd like to hear from you. Address all correspondence to:

Paratronics, Inc.

800 Charcot Avenue

San Jose, CA 95131

Table 1-1

COMPARISON OF MODEL 100A LOGIC ANALYZER WITH HP-1607

| <u>FEATURE</u>                | <u>HP-1607<br/>LOGIC ANALYZER</u> | <u>MODEL 100A<br/>LOGIC ANALYZER</u>           | <u>WITH MODEL 10<br/>TRIGGER EXPANDER</u> |

|-------------------------------|-----------------------------------|------------------------------------------------|-------------------------------------------|

| DISPLAY TYPE                  | TRUTH TABLE                       | TRUTH TABLE                                    | SAME                                      |

| DISPLAY FORMAT                | HEX/OCTAL                         | HEX/OCTAL                                      | SAME                                      |

| DATA COLLECTION               | PRE-TRIGGER &<br>POST-TRIGGER     | PRE-TRIGGER &<br>POST-TRIGGER                  | SAME                                      |

| DISPLAY MODES                 | SINGLE/REPEAT                     | SINGLE/REPEAT                                  | SAME                                      |

| INTENSIFIED TRIGGER           | YES                               | YES                                            | SAME                                      |

| CLOCK EDGE SELECT             | RISING/FALLING                    | RISING/FALLING                                 | SAME                                      |

| EXTERNAL TRIG. PULSE          | YES                               | YES                                            | SAME                                      |

| TRIGGER WORD                  | 16 BITS                           | 8 BITS                                         | 24 BITS                                   |

| QUALIFIERS                    | TRIGGER <u>OR</u> CLOCK           | -                                              | TRIGGER <u>&amp;</u> CLOCK                |

| DELAY                         | 0 - 99,999 CLOCKS                 | -                                              | 0 - 999 CLOCKS OR<br>TRIGGER WORDS        |

| DISPLAY SIZE                  | 2 BYTES BY 16 DEEP                | 1 BYTE BY 16 DEEP                              | 3 BYTES BY 16 DEEP<br>(1 BYTE AT A TIME)  |

| LOGIC FAMILY<br>COMPATIBILITY | TTL, DTL, RTL, MOS,<br>CMOS, ECL  | TTL, DTL, RTL, MOS, SAME AS MODEL 100A<br>CMOS |                                           |

| DATA COLLECTION RATE          | 20MHz                             | 8MHz                                           | SAME AS MODEL 100A                        |

| MAP MODE                      | YES                               | NO                                             | -                                         |

| AUXILIARY MEMORY              | YES                               | NO                                             | -                                         |

| BLANKING OUTPUT               | 10 VOLTS MAX                      | 30 VOLTS MAX                                   | SAME AS MODEL 100A                        |

| EXT. SCOPE REQ'D              | YES                               | YES                                            | SAME AS MODEL 100A                        |

| SCOPE COUPLING                | DC RECOMMENDED                    | AC OR DC                                       | SAME AS MODEL 100A                        |

| WEIGHT                        | 14 POUNDS                         | 5 POUNDS                                       | 3 POUNDS                                  |

| POWER                         | 120 WATTS                         | 7.5 WATTS                                      | 2 WATTS                                   |

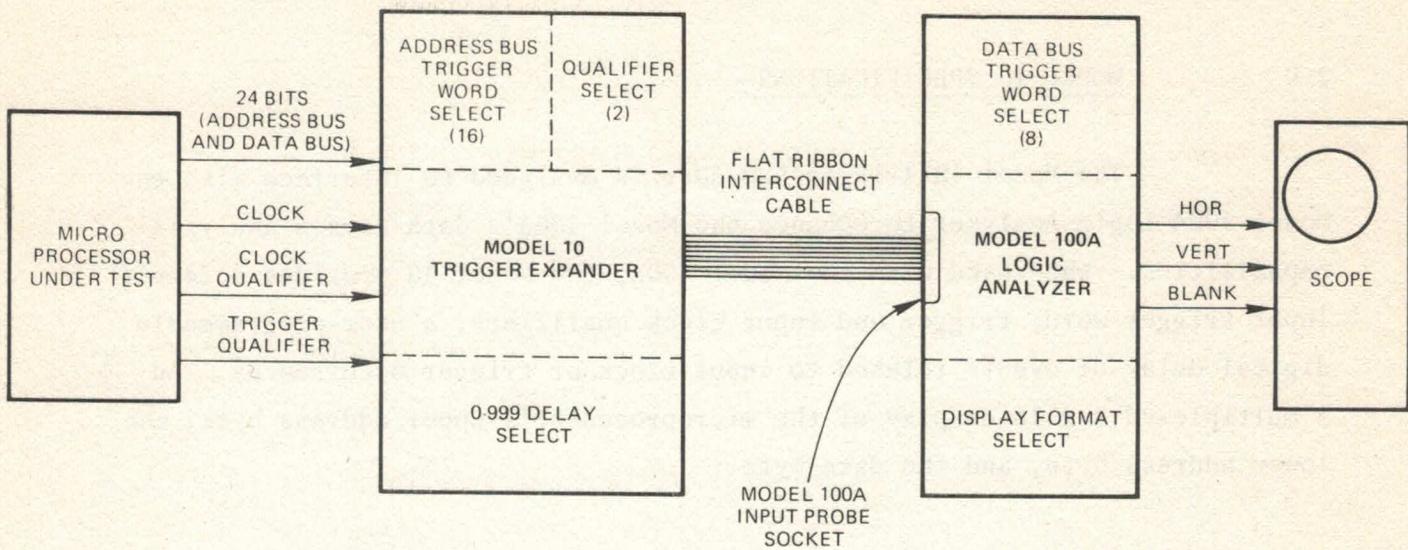

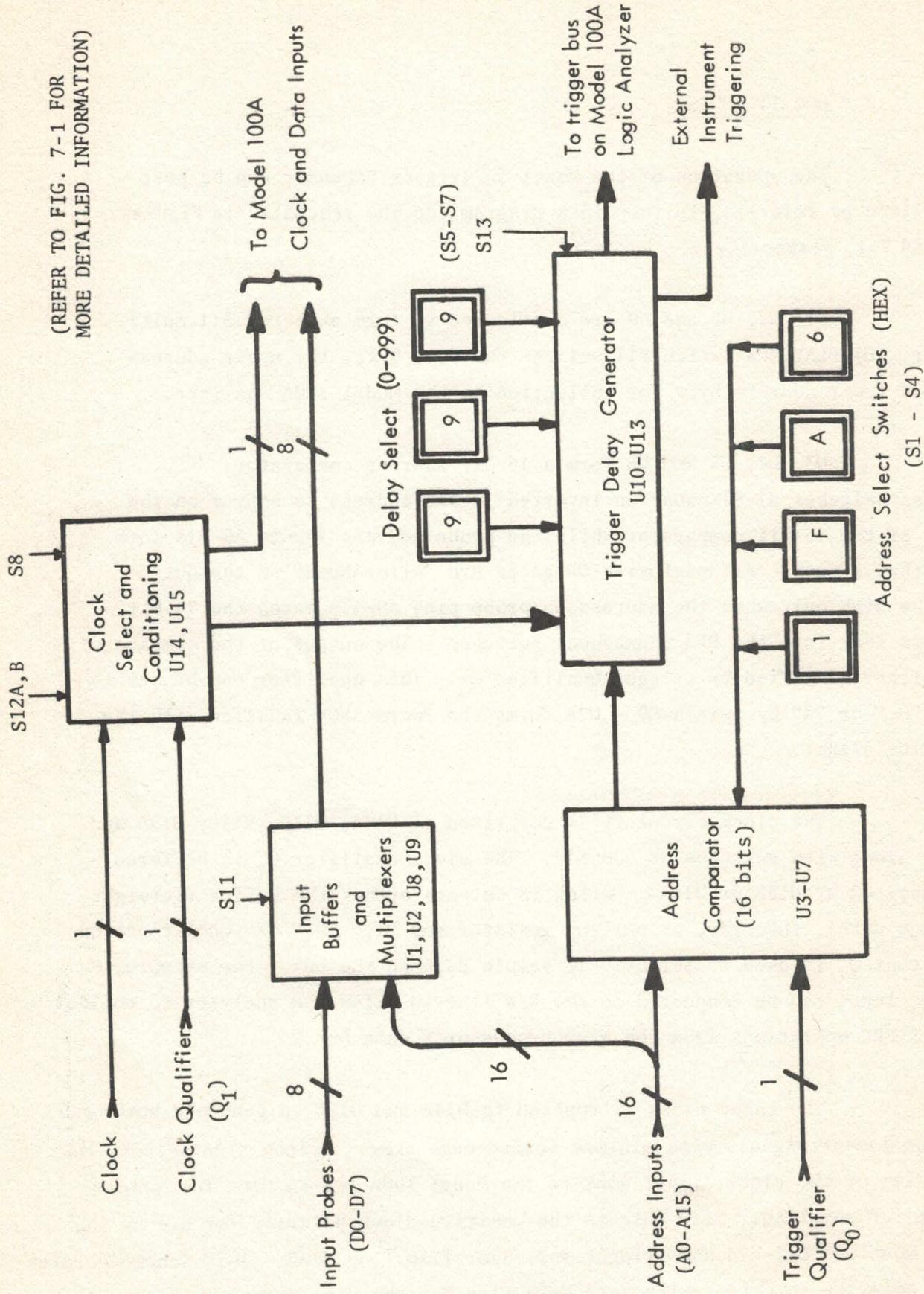

The Model 10 Trigger Expander is designed to interface with the Model 100A Logic Analyzer to enhance the Model 100A's data domain analysis capabilities. When used with the Model 100A, the Model 10 provides a 24-bit input trigger word, trigger and input clock qualifiers, a user-programmable digital delay of events related to input clock or trigger occurrences, and a multiplexed 8 x 16 display of the microprocessor's upper address byte, the lower address byte, and the data byte.

The controls for all of the above functions, with the exception of the trigger word switches for the data byte, are located on the Model 10. (The data byte is controlled by the 8 trigger word switches on the Model 100A.)

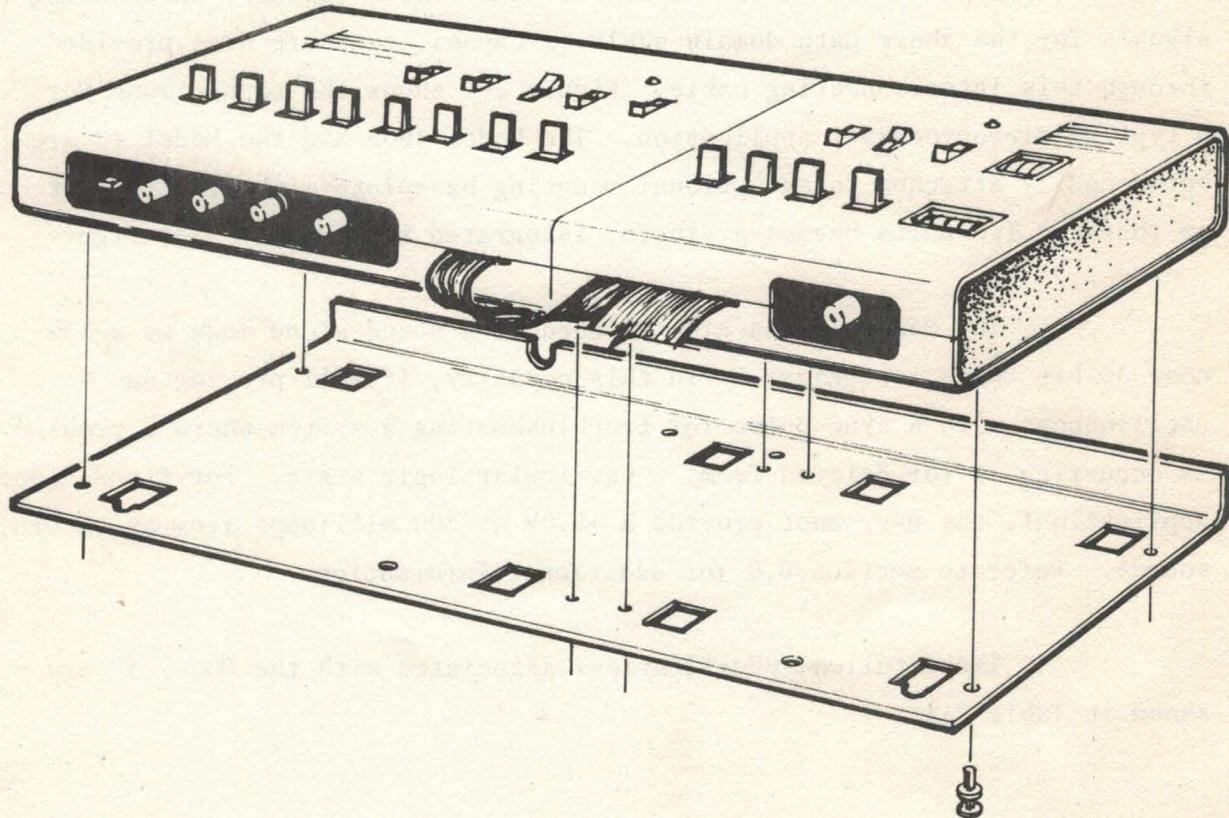

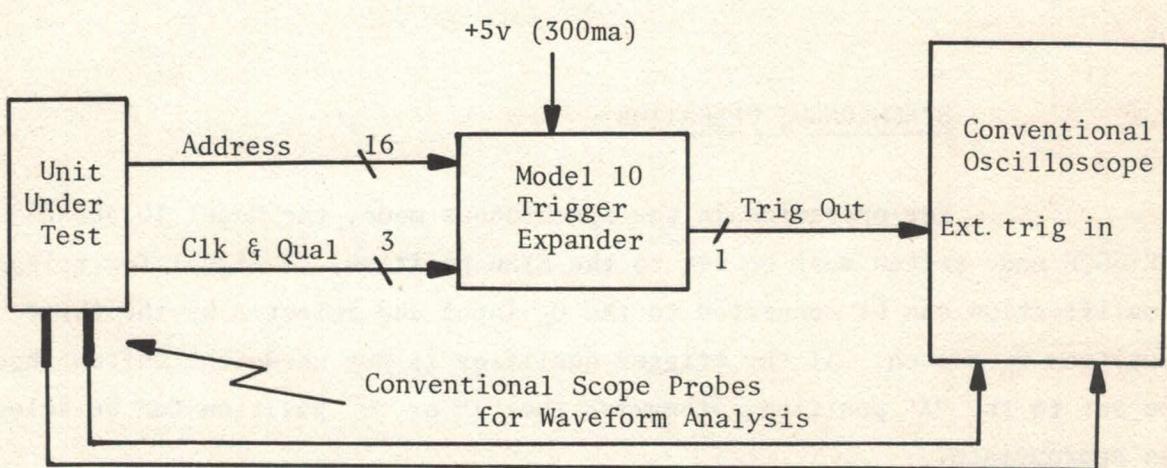

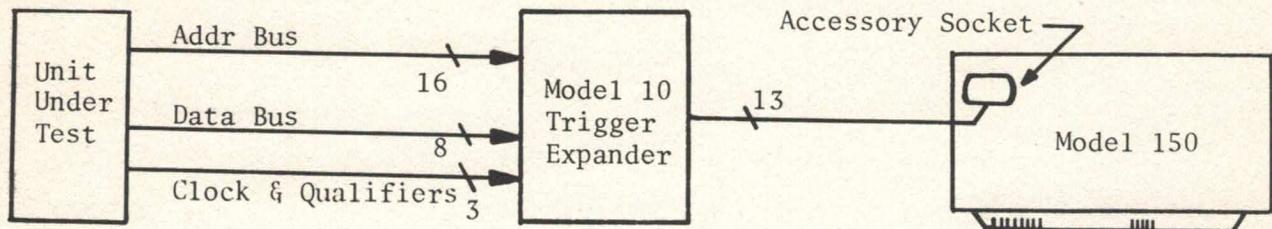

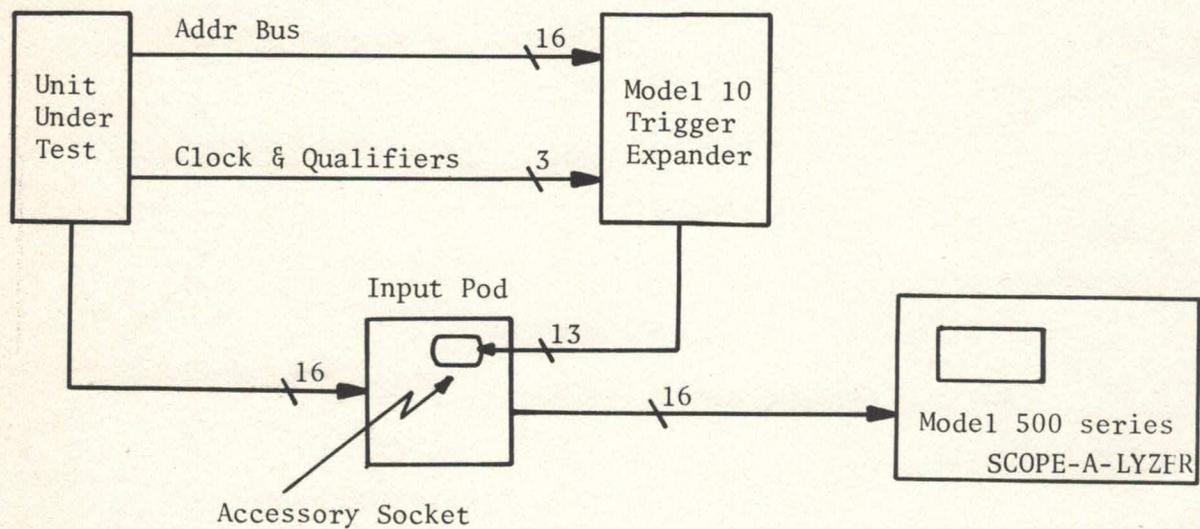

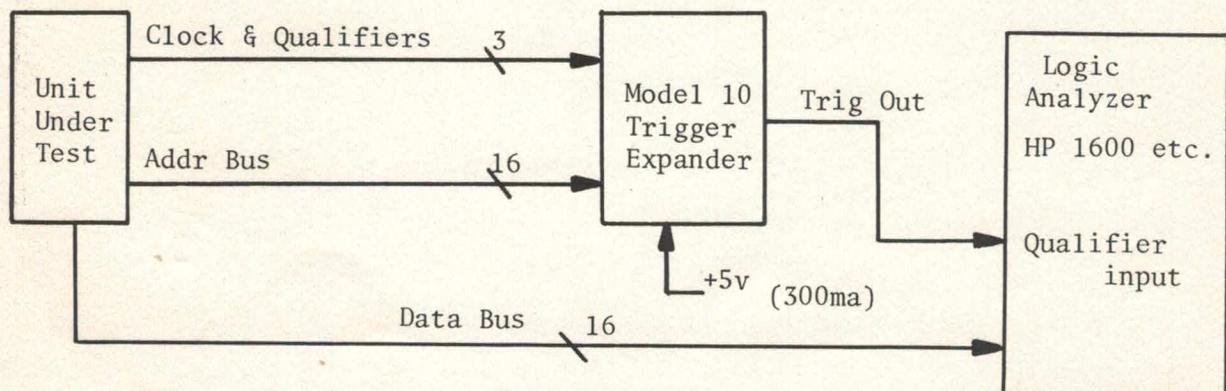

The Model 10 is powered through a flat ribbon cable which plugs into the input probe socket of the Model 100A. The necessary "handshaking" signals for the above data domain analysis capabilities are also provided through this interconnecting cable. Figure 2-1 shows the connections for a typical microprocessor application. The Model 100A and the Model 10 are both readily attached to an optional mounting baseplate with plastic fasteners, so that the two units become a single, integrated instrument. See Figure 2-2.

The Model 10 can also be used in a stand-alone mode as a low-cost 16-bit "word recognizer." In this capacity, it will provide an oscilloscope with a sync pulse for troubleshooting a system where a problem is occurring at (or delayed from) a particular logic state. For stand-alone applications, the user must provide a +5.0V at 300 milliamps from an external source. Refer to Section 8.0 for additional information.

The detailed specifications associated with the Model 10 are shown in Table 2-1.

Fig. 2-1. Model 10 and Model 100A electrical connections for a typical microprocessor application.

Fig. 2-2. The optional mounting baseplate interconnects the two units so that they become a single, integrated instrument.

Table 2-1

## SPECIFICATIONS

|                                |                                                                                                                                                                                                                                                                    |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Scope Requirements:            | Any laboratory or field oscilloscope with 100 KHz bandwidth and an external Horizontal (X) input. A blanking input is useful but not mandatory.                                                                                                                    |

| Address Triggering:            | 16 buffered address inputs. Address selectable with 4-digit HEX thumbwheel switches.                                                                                                                                                                               |

| Address Input Load:            | Logic 0: -0.5V to +1.6V; -720 microamps max.<br>Logic 1: +1.6V to +15V; +100 microamps max.                                                                                                                                                                        |

| Data Word Triggering:          | 8 buffered data inputs. Data word is selectable from eight 3-position trigger word switches on Model 100A ("1," "0," or "X").                                                                                                                                      |

| Data Word Load:                | Logic 0: -0.5V to +1.6V; -360 microamps max.<br>Logic 1: +1.6V to +15V; +100 microamps max.                                                                                                                                                                        |

| Display Multiplexing:          | Provided by 3-position switch which multiplexes the upper address byte, the lower address byte, or the data byte into the Model 100A's data memory. This feature permits the viewing of 3 individual 8 x 16 truth tables without moving the Model 10 input probes. |

| Input Clock:                   | Positive or negative edge triggering.                                                                                                                                                                                                                              |

| Input Clock Load:              | (Same as address input load.)                                                                                                                                                                                                                                      |

| Maximum Clock Frequency:       | 8 MHz                                                                                                                                                                                                                                                              |

| Minimum Clock Pulse Width:     | 50 ns (active edge to inactive edge)                                                                                                                                                                                                                               |

| Address or Data Hold Time:     | 0 ns after active clock edge                                                                                                                                                                                                                                       |

| Address or Data Set-up Time:   | 25 ns before active clock edge.                                                                                                                                                                                                                                    |

| Clock Qualifier:               | Permits READ, STORE, I/O and other selected operations which are associated with a particular clock to be collected for display. Controlled by a 3-position switch ("1," "0," or "X").                                                                             |

| Address Qualifier:             | Permits machine states associated with a particular address to be collected for display. Controlled by a 3-position switch ("1," "0," or "X").                                                                                                                     |

| Address Qualifier Set-Up Time: | 25 ns before active clock edge.                                                                                                                                                                                                                                    |

| Address Qualifier Hold Time:   | 0 ns after active clock edge.                                                                                                                                                                                                                                      |

| Qualifier Load:                | (Same as data word load.)                                                                                                                                                                                                                                          |

| Digital Delay:                 | Selectable by a 3-digit thumbwheel switch (0-999 events).                                                                                                                                                                                                          |

| Delay Modes:                   | CLOCK (for paging through 1000 program steps); and TRIGGER (for permitting the machine to loop up to 1000 times before display).                                                                                                                                   |

| Address Trigger Modes:         | SYNCHRONOUS, OFF, or ASYNCHRONOUS.                                                                                                                                                                                                                                 |

| Trigger Output:                | Auxiliary TTL pulse which occurs when valid trigger word is detected. (This is main output for stand-alone operation.)                                                                                                                                             |

| Trigger Indicator:             | LED on Model 10 indicates that unit is waiting for valid trigger to occur.                                                                                                                                                                                         |

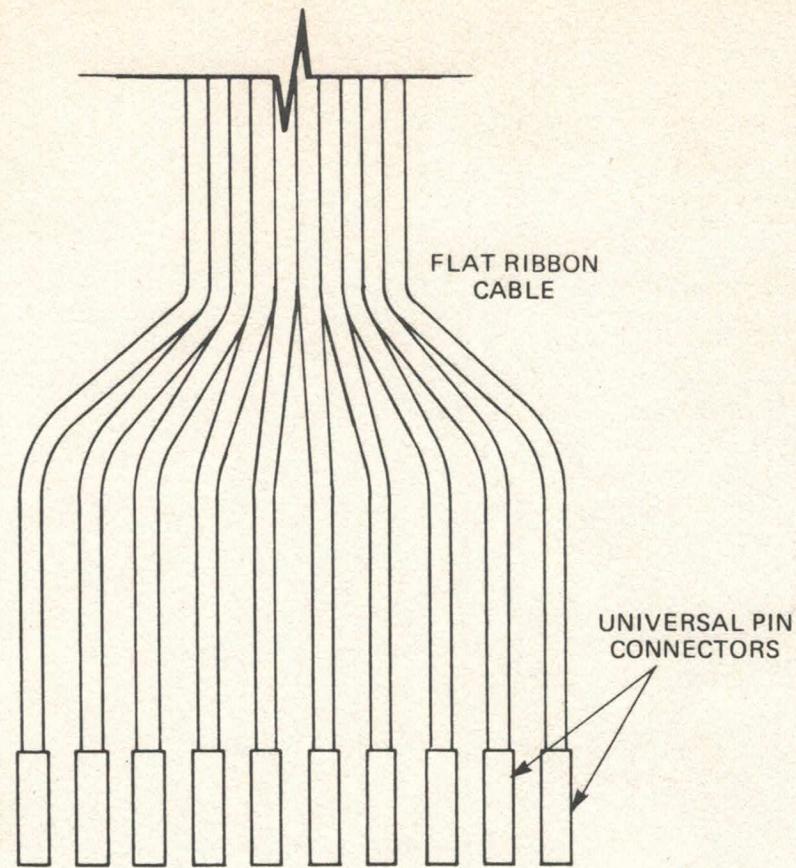

| Input Probes:                  | Multi-wire, color-coded flat ribbon cable terminated in gold-plated "universal" pin connectors.                                                                                                                                                                    |

| Model 100A Connection:         | 16-pin flat ribbon cable from Model 10 plugs into Model 100A input probe socket (field installable).                                                                                                                                                               |

| Power:                         | Model 100A provides power through above cable. (+5V @ 300 milliamps when used in stand-alone mode.)                                                                                                                                                                |

| Mounting:                      | Optional baseplate permits Model 10 to be mechanically mated to Model 100A so that the two units become a single, integrated instrument.                                                                                                                           |

| Weight:                        | 3 pounds.                                                                                                                                                                                                                                                          |

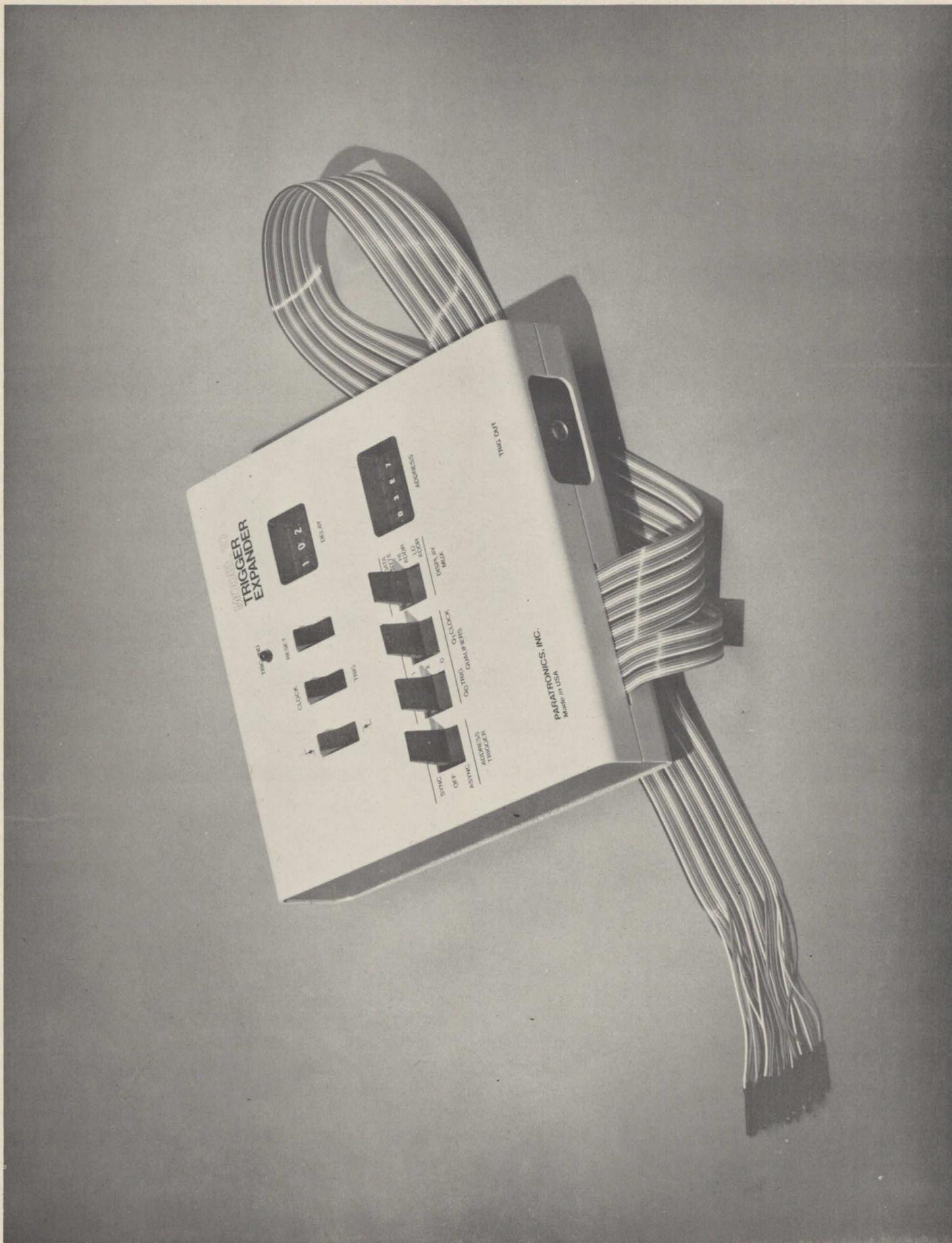

The controls of the Model 10 are shown in the photo of Figure 3-1. In most cases, the description of these controls pertains to the use of the Model 10 connected to the Model 100A.

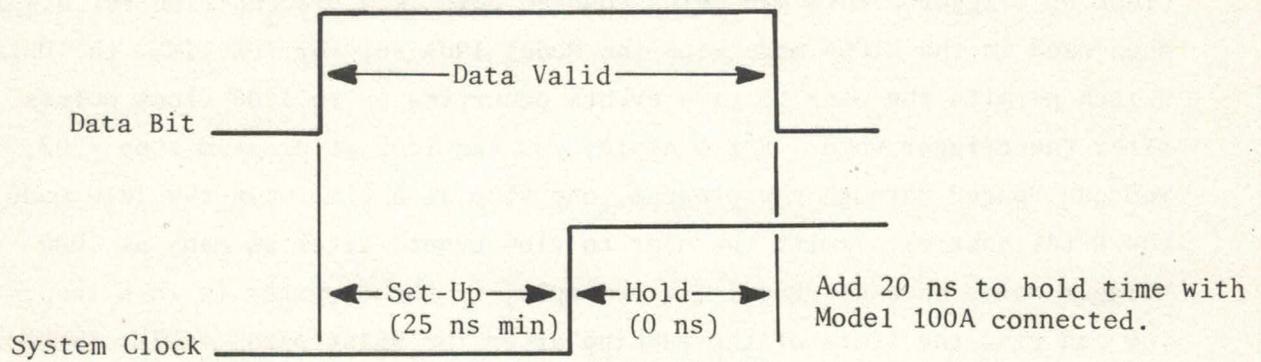

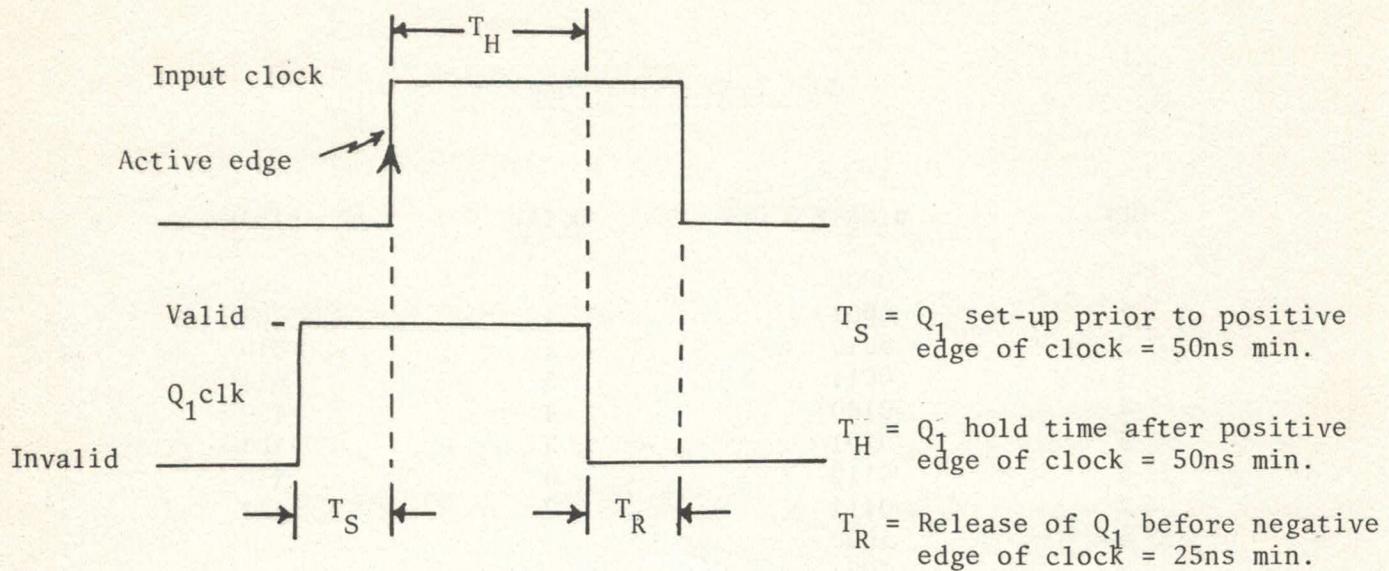

RISING (F)/FALLING (L) CLOCK EDGE SELECT - This control determines the active edge of the input clock of the system-under-test. In some circuits, data are valid on the rising edge of the system clock, while in others, the negative clock edge determines the validity of the data. IN ORDER TO OBTAIN A MEANINGFUL DISPLAY, THE CLOCK EDGE SELECT CONTROL ON THE MODEL 10 MUST BE SET TO THE CORRECT POSITION. ALSO, THE CORRESPONDING CONTROL ON THE MODEL 100A MUST ALWAYS BE SET TO THE FALLING (L) EDGE POSITION. Figure 3-2 summarizes the above statement. Also, be sure and observe the timing relationships shown in the figure. (Note: With the Model 10 in the stand-alone mode, the hold time for data after the active clock edge is 0 ns. When the Model 10 is used with the Model 100A, the hold time for the two units together is approximately 20 ns.)

CLOCK/TRIG - This mode switch selects whether the digital delay control on the Model 10 refers to clock pulses or trigger occurrences. For example, the CLOCK mode is useful for paging through long programs; while the TRIG mode can be used to display the state of the machine after it has looped "n" times. (These concepts are explained further below.)

RESET - This switch functions in parallel with the one on the Model 100A. It is used when the Model 100A is in the SINGLE mode to clear the display and "arm" the analyzer for the capturing of the next truth table. EITHER RESET SWITCH CAN BE USED TO PERFORM THIS FUNCTION. (The Model 10 has the duplicate RESET switch for stand-alone operation. Refer to Section 8.0 for additional details.)

Fig. 3-1. The controls of the Model 10 Trigger Expander.

#### POSITIVE CLOCK EDGE SYSTEMS

Note:

Model 100A Clock Edge Select Control must always be in falling (▼) edge position.

#### NEGATIVE CLOCK EDGE SYSTEMS

Fig. 3-2. In order to collect meaningful data, the proper input clock edge must be chosen on the Model 10.

DELAY - This three station thumbwheel switch selects the number of clock pulses or trigger words (0-999) that must occur before the data will be displayed by the Model 100A. (The CLOCK/TRIG mode switch determines whether clock or trigger events are being counted down as a precondition for display.) When used in the CLOCK mode with the Model 100A set for POS TIME, the DELAY switch permits the user to view events occurring up to 1000 clock pulses after the trigger word. For example, you can look at program step #702, or you can "page" through the program, one step at a time. In the TRIG mode, the DELAY control permits the user to view events after as many as 1000 trigger words have occurred. For example, if the computer is in a loop, you can view the state of the machine after the 951st pass. NOTE: WHEN THE DELAY CONTROL IS SET AT "000," NO DELAY TAKES PLACE. THE CLOCK/TRIG SWITCH MAY BE SET TO EITHER THE CLOCK OR TRIGGER POSITIONS. When the Model 100A is set for NEG TIME and the Model 10 in the CLOCK mode, you can "move" the trigger word up from the bottom of the screen towards the top so that events before and after the trigger can be observed. (Refer to Section 4.0 for a discussion concerning the function of the delay control when the setting exceeds 016.) NOTE: WHEN USING THE DELAY FEATURE OF THE MODEL 10, THE INTENSIFIED FIRST OR LAST WORDS IN THE TRUTH TABLE HAVE NO MEANING EXCEPT TO INDICATE WHETHER THE MODEL 100A IS IN THE POS OR NEG TIME MODE. THE TRIGGER WORD ITSELF WILL NO LONGER BE INTENSIFIED. (HINT: FOR MANY SCOPES, IT IS POSSIBLE TO DISCONNECT THE BLANKING INPUT AND REMOVE THE INTENSIFIED WORD, IF DESIRED, WITHOUT AFFECTING THE READABILITY OF THE DISPLAY.)

ADDRESS TRIGGER - This three-position switch determines the function of trigger qualifier ( $Q_0$  TRIG) and the hexadecimal ADDRESS switch as follows:

SYNC Mode - THIS IS THE NORMAL MODE FOR OPERATING THE MODEL 10 WITH THE MODEL 100A. In this mode, the state of the system's address bus and the  $Q_0$  qualifying signal are sampled synchronously using the input clock. (The resulting TRIG OUT pulse, described below, is also synchronous with the input clock.)

OFF Mode - This switch position places the input address lines and the  $Q_0$  qualifier into the "don't care" state so that they have no affect on triggering. Thus, in this mode, triggering is solely a function of the Model 100A's eight trigger switches.

ASYNC Mode - This switch position should be used only when the Model 10 is used in the stand-alone mode as a 16-bit word recognizer. The signal at TRIG OUT is then a TTL level which occurs anytime the 16 bits of the input trigger word plus the trigger qualifier ( $Q_0$ ) are satisfied. Note, in this mode, the input clock line has no effect.

$Q_0$  TRIG - This switch controls the operation of a 1-bit input line used to qualify the input address bus. The switch has three positions as follows: "1," "0," and "X." In the "X" position, the qualifying line is turned off. In either of the other two positions, it determines the active level that must be provided by the microprocessor-under-test before address triggering can occur. For example, by connecting the  $Q_0$  input to a microprocessor control line, such as the write signal, triggering of the analyzer will occur only when a STORE operation is performed at the selected input address. Note that the  $Q_0$  qualifier functions as an enable signal and is not displayed.

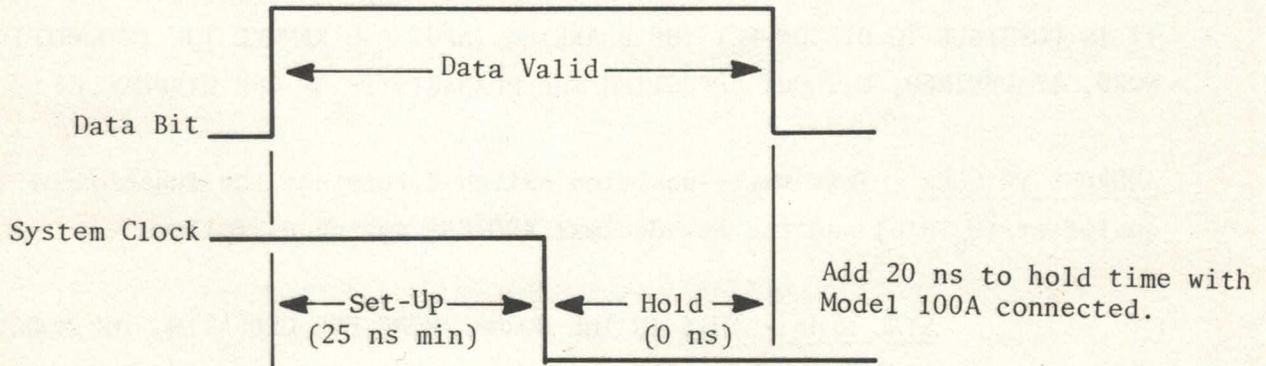

$Q_1$  CLOCK - This switch controls a 1-bit input line used to qualify the input clock. Like the  $Q_0$  TRIG switch, it also has three positions: "1," "0," and "X." In the "X" position,  $Q_1$  is disabled and the clock is not qualified. In either of the other two positions, it determines the active level that must be provided by the microprocessor-under-test before an input clock pulse can be received by the Model 10. By connecting the associated  $Q_1$  input line to the appropriate control signal, only data or addresses occurring when the  $Q_1$  line is enabled will be clocked into the Model 10. For example, in Motorola 6800 applications, the  $Q_1$  line can be connected to the signal "VMA" (Valid Memory Address), and the  $Q_1$  CLOCK switch can be set to the "1" state. With

this set-up, only 6800-directed bus activity will be monitored. Note that the  $Q_1$  qualifier, like the  $Q_0$  qualifier, functions as an enable signal and is not displayed. See Figure 3-3 for  $Q_1$  timing requirements.

DISPLAY MUX - This three-position switch multiplexes the microprocessor's data byte, lower address byte, and upper address byte into the Model 100A's 8-bit data memory. With the Model 100A in the REPEAT mode, changing this switch position on the Model 10 will automatically cause three 16-word truth tables associated with the lower and upper address bytes and the data byte to be displayed. IN MOST APPLICATIONS, THE MODEL 100A'S TRIGGER SWITCHES SHOULD BE IN THE "X" (DON'T CARE) POSITION WHEN USING THIS FUNCTION. REFER TO SECTIONS 4.0 AND 6.0 FOR ADDITIONAL INFORMATION CONCERNING TRIGGERING.

ADDRESS - This is a four-digit thumbwheel switch which determines the value of the 16-bit address trigger word. This switch is coded in hexadecimal. (Refer to the chart in Table 3-1 to convert other address codes.) NOTE: UNUSED ADDRESS INPUT LINES WILL ASSUME THE "1" STATE. HOWEVER, IF NOISE ON THESE LINES IS A PROBLEM WITH SOME SYSTEMS, IT IS RECOMMENDED THAT THESE UNUSED INPUTS BE GROUNDED AND TREATED AS "0's" WHEN USING THE HEX THUMBWHEEL SWITCH.

TRIG OUT - This is a BNC-type connector which provides a TTL output whenever the conditions described below are met. When the ADDRESS TRIGGER switch is in the SYNC mode, an active high pulse will appear at this output at the instant all input triggering conditions are met. When the ADDRESS TRIGGER switch is in the OFF mode, the BNC connector gives the user direct access to the internal trigger bus of the Model 100A. And finally, when the ADDRESS TRIGGER switch is in the ASYNC mode, an active high TTL level will appear at this output whenever the 16-bit address and  $Q_0$  qualifier inputs are satisfied. This mode of operation is primarily intended for applications requiring the stand-alone word recognizing capabilities of the Model 10. (Refer to Section 8.0 for additional details.)

#### POSITIVE CLOCK EDGE SYSTEMS:

$Q_1$  MUST "BRACKET" RISING CLOCK EDGE

#### NEGATIVE CLOCK EDGE SYSTEMS:

$Q_1$  MUST "BRACKET" FALLING CLOCK EDGE

Fig. 3-3. Clock qualifier ( $Q_1$ ) timing requirements.  $Q_1$  can be selected as "1," "0," or "X."

Table 3-1

CODE CONVERSION CHART

| <u>HEX</u> | <u>BINARY</u> | <u>OCTAL</u> | <u>BINARY</u> |

|------------|---------------|--------------|---------------|

| 0          | 0000          | 0            | 000           |

| 1          | 0001          | 1            | 001           |

| 2          | 0010          | 2            | 010           |

| 3          | 0011          | 3            | 011           |

| 4          | 0100          | 4            | 100           |

| 5          | 0101          | 5            | 101           |

| 6          | 0110          | 6            | 110           |

| 7          | 0111          | 7            | 111           |

| 8          | 1000          |              |               |

| 9          | 1001          |              |               |

| A          | 1010          |              |               |

| B          | 1011          |              |               |

| C          | 1100          |              |               |

| D          | 1101          |              |               |

| E          | 1110          |              |               |

| F          | 1111          |              |               |

Example: Convert  $(0F0A)_{\text{HEX}}$  to octal equivalent.

| Procedure: |  |  |  | <u>0</u> | <u>F</u> | <u>0</u> | <u>A</u> | HEX Word       |

|------------|--|--|--|----------|----------|----------|----------|----------------|

|            |  |  |  | 0000     | 1111     | 0000     | 1010     | HEX Grouping   |

|            |  |  |  | 0 000    | 111      | 100      | 001      | OCTAL Grouping |

|            |  |  |  | 0 0      | 7        | 4        | 1        | OCTAL Word     |

Thus  $(0F0A)_{\text{HEX}} = (7412)_{\text{OCT}}$

TRIG IND - This is a LED indicator on the front panel of the Model 10 which operates in parallel with the indicator on the Model 100A. In the OFF and SYNC modes, an illuminated LED signifies that the Model 100A/Model 10 integrated package is waiting for all trigger, qualifier, and delay requirements to be satisfied. When these conditions are met, both LEDs will turn off. In the ASYNC mode, the LEDs have no functions and will always remain on. The LED on the Model 10 is particularly useful when operating the unit in the stand-alone mode. In this mode, it provides information about the occurrence of a particular logic state.

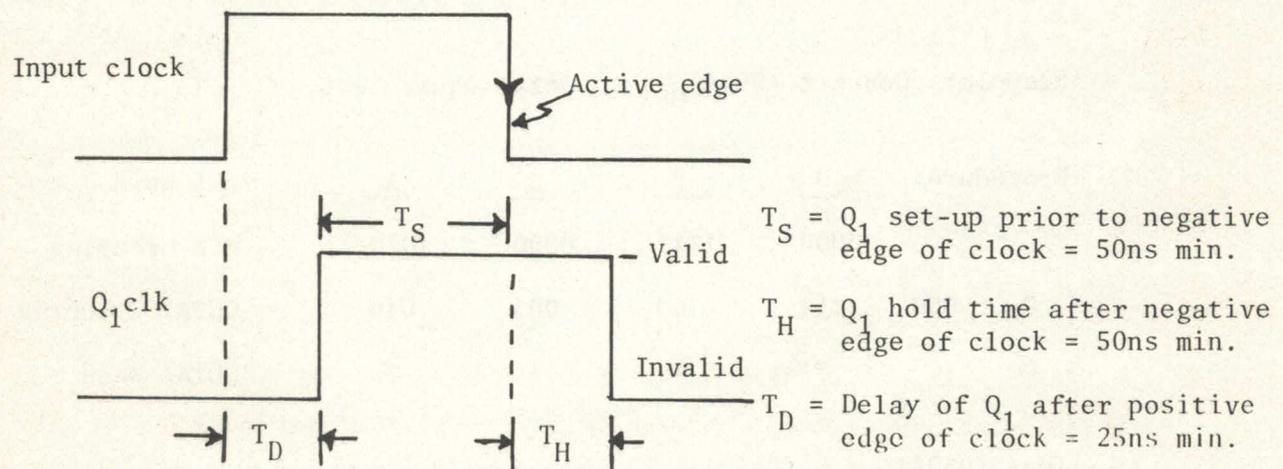

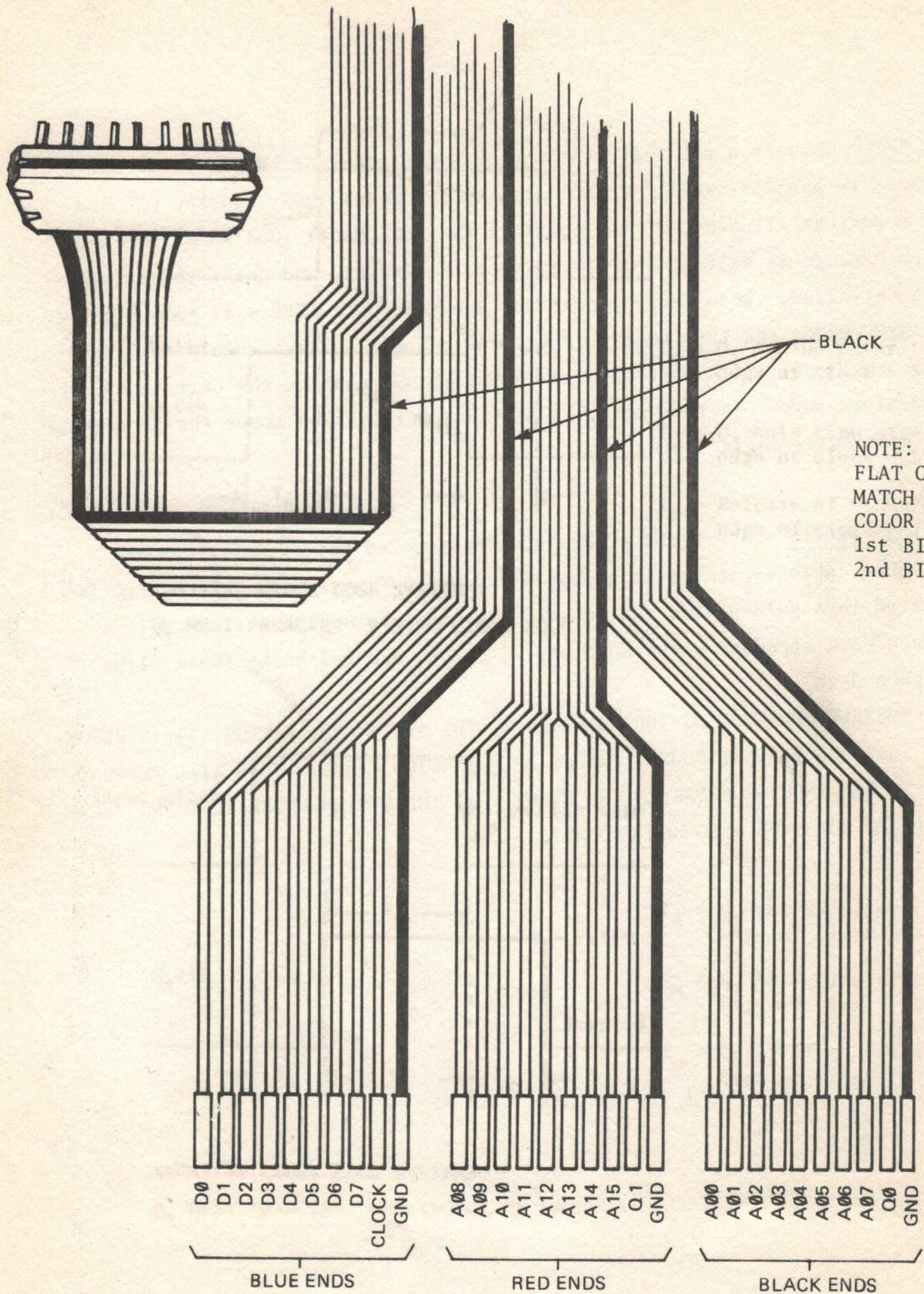

INPUT DATA PROBES - The input probes are constructed out of multi-colored flat ribbon cable separated in groups as shown in Figure 3-4a. Each wire is terminated in a gold-plated "universal" pin connector which will readily interface with standard wirewrap pins, IC clips, and E-Z hooks (ball clips). See Figure 3-4b.

NOTE: WHENEVER CONNECTING THE MODEL 10 TO THE SYSTEM-UNDER-TEST, IT IS RECOMMENDED THAT THE BLACK (GROUND) PROBES BE CONNECTED FIRST. THIS WILL PREVENT DAMAGE TO THE INPUT BUFFERS IN THE EVENT THAT THE SYSTEM-UNDER-TEST AND THE MODEL 10 DO NOT HAVE A COMMON GROUND.

Fig. 3-4a. Model 10 input probe assembly signal definitions.

Fig. 3-4b. Data probe interfacing techniques.

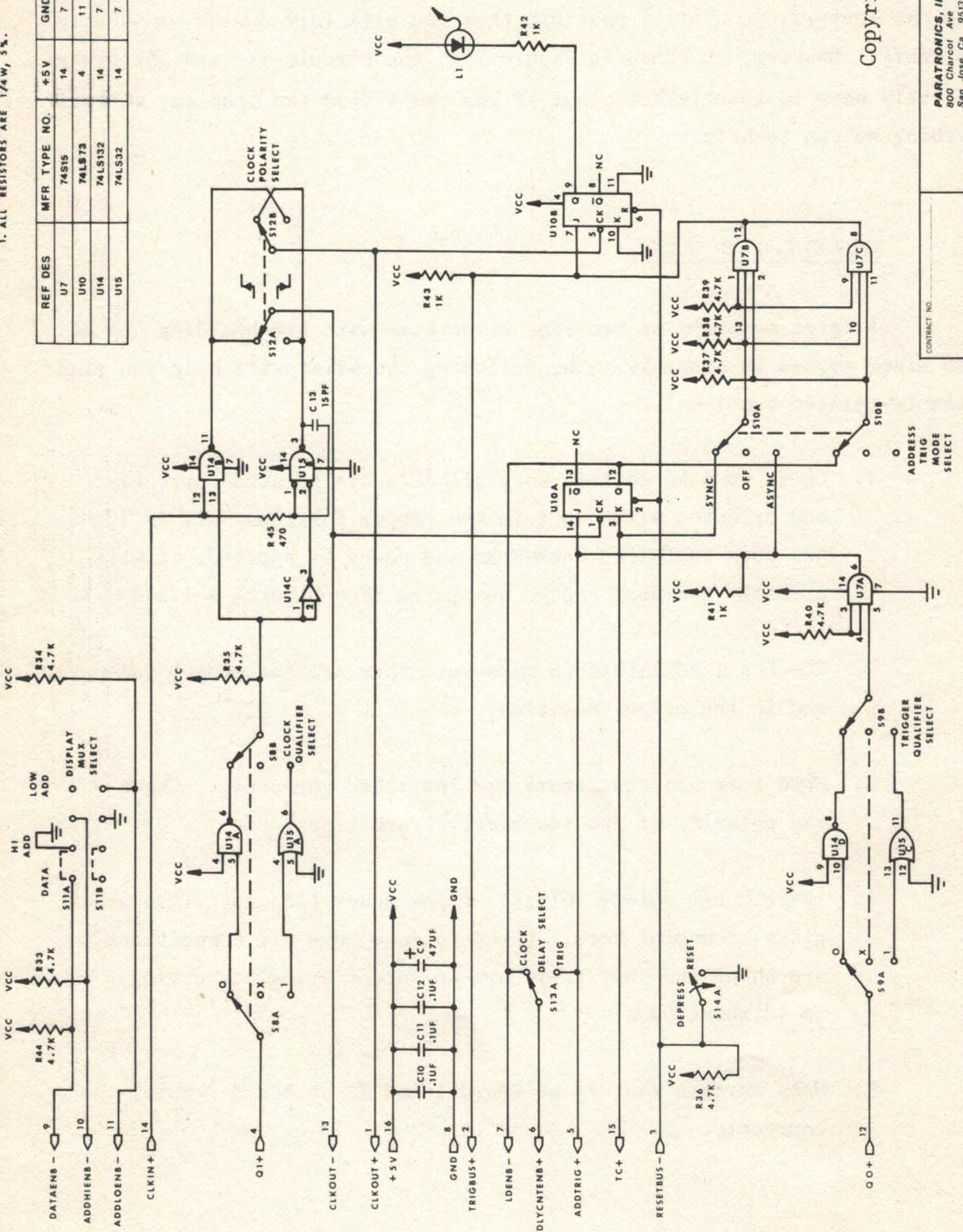

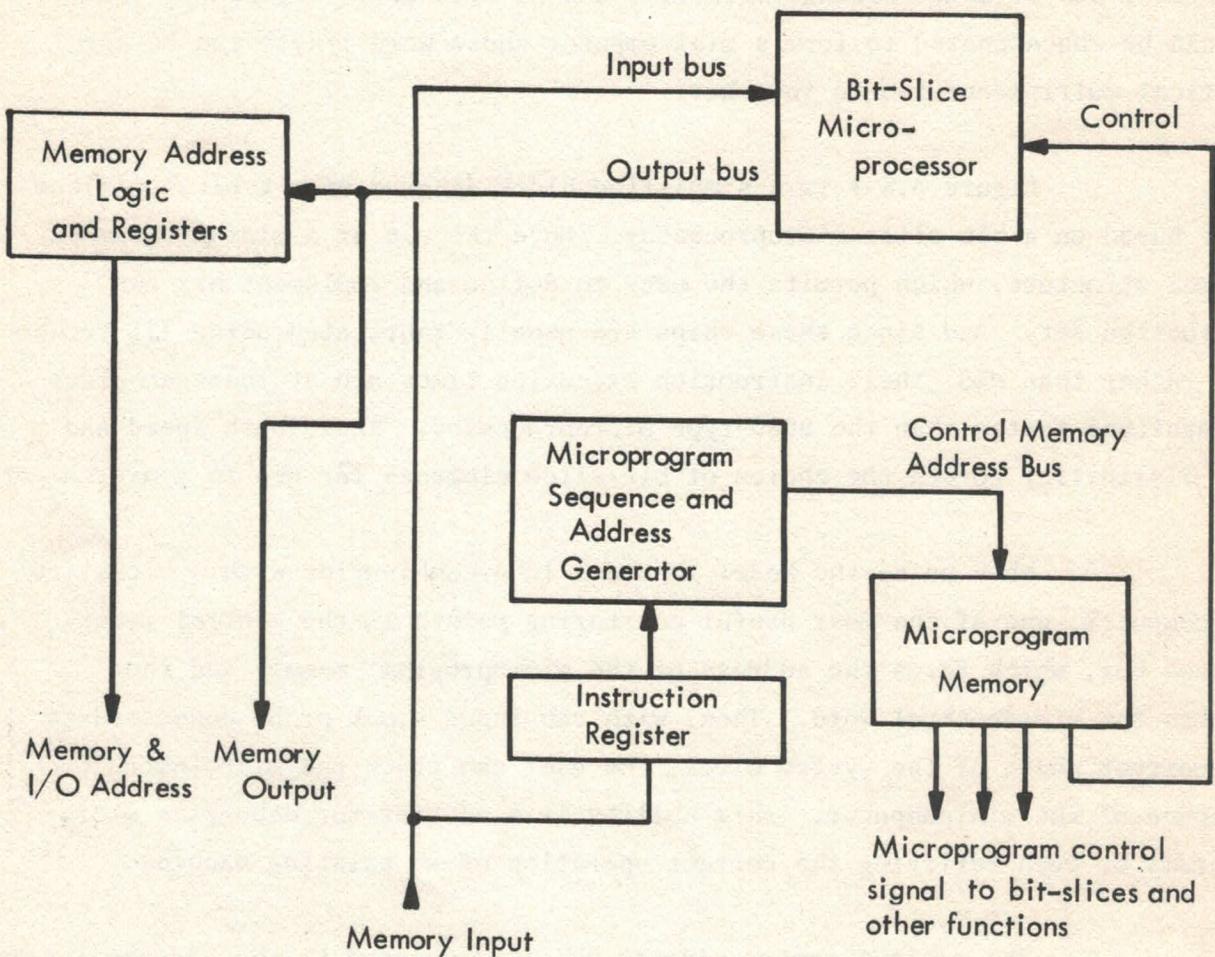

The operation of the Model 10 Trigger Expander can be best understood by referring to the block diagram and the schematic in Figures 4-1 and 7-1, respectively.

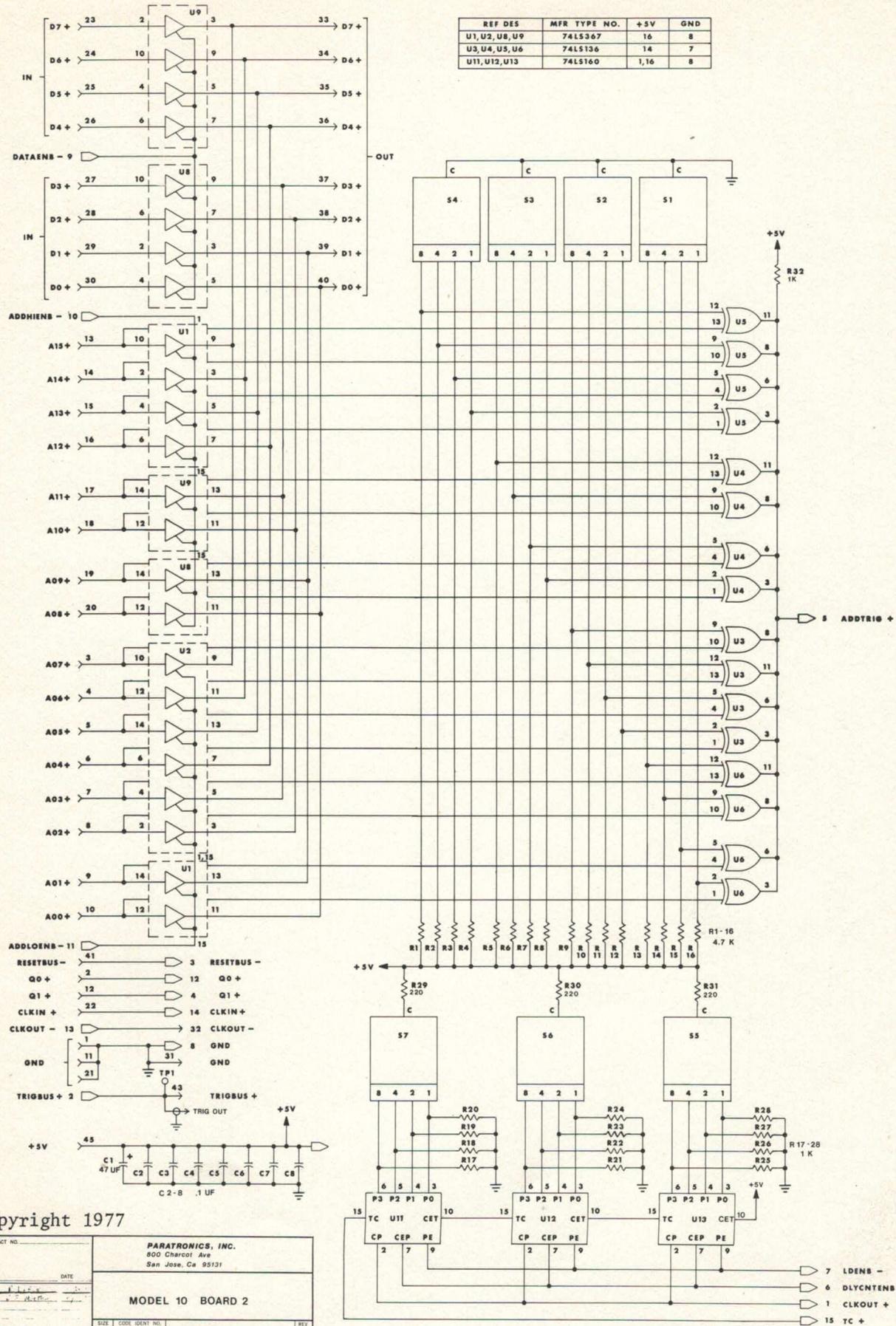

U1, U2, U8 and U9 are configured to form an octal 3:1 multiplexer. DISPLAY MUX switch S11 selects the data byte, the upper address byte or lower address byte for collection by the Model 100A Analyzer.

U3, U4, U5 and U6 form a 16-bit address comparator. HEX address switches S1-S4 cause an inverted 16-bit address to appear on the input of the 16-bit comparator while the probe address inputs A0-A15 form the other inputs. All exclusive-OR gates are "wire-ANDED" so the output will be high only when the address on probe pins A0-A15 match the 16-bit address sent into the HEX thumbwheel switches. The output of the comparator is further qualified by trigger qualifier  $Q_0$ . This qualifier can be set to "1," "0," or "X" by switch S9. U7A forms the "wire-AND" function with the ADDTRIG+ signal.

The clock circuitry is comprised of U14A, U14B, U14C, U15A and U15B, along with switches S8 and S12. The clock qualifier  $Q_1$  is buffered or inverted by U15A or U14A. Switch S8 selects either the buffer (straight-through path), inverter, or pull-up resistor for "1," "0," "X" qualification. Note that  $Q_1$  is used to selectively sample data on the bus. For example, the  $Q_1$  input can be connected to the R/W line to allow the analyzer to collect only STORE operations from the microprocessor's data bus.

The input clock is applied to U14B and U15B to generate both true and complement signals with minimum active edge skew. Switch S12A selects the inversion of the clock signal sent to the Model 100A and to U10A for address comparator sampling. S12B selects the positive clock polarity for use by the delay counters U11-U13 and trigger indicator flip-flop U10B. This scheme permits clock polarity selection with zero hold time for the data relative to the clock for the Model 10 in the stand-alone mode. (NOTE, HOWEVER, WHEN USING THE

Fig. 4-1. Block diagram of Model 10 Trigger Expander.

MODEL 10 WITH THE MODEL 100A, THE MODEL 100A CLOCK POLARITY SWITCH SHOULD ALWAYS BE SET TO THE FALLING EDGE (▼) POSITION.)

U11-U13 and switches S5-S7 comprise the digital delay function of the trigger expander. Switches S5-S7 and resistors R17-R31 generate a "compliment of 9's compliment" 3-digit BCD number which is loaded into binary UP counters, U11-U13. This loading is performed every clock cycle until the trigger occurs and U10A is set. The counter mode controls are then switched to the count mode and UP counting proceeds on subsequent clock pulses. If delay mode switch S13A is set to the CLOCK position, the counter will be incremented each clock cycle after triggering has occurred. If S13A is in the TRIG position, the counter is incremented only when a valid address trigger word is present. In this way, it is possible to set the address switches--say at the beginning of a loop--and delay triggering of the analyzer for an integral number of loop iterations. For microprocessor loop analysis, this feature is far more useful than counting clock pulses particularly if the number of clock pulses per loop is not constant.

When the counter reaches the maximum count (999), TC+ goes high and enables the analyzer trigger bus via AND gates U7B and U7C. The inputs of this gate are controlled by switch S10. In the SYNC position, gates U7B and U7C satisfy the trigger bus when trigger flip-flop U10A has been set and the delay counter has reached terminal count (i.e., TC+ is high). Then, when data inputs to the Model 100A agree with the Model 100A input switches, the analyzer will trigger. When switch S10 is in the OFF position, all inputs to gates U7B and U7C are a logic "1" and the Trigger Expander has no effect on the triggering of the Model 100A. In the ASYNC position, S10 directly passes the address trigger bus ADDTRIG+ to the BNC output jack via gates U7B and U7C. This mode is useful when the Model 10 is functioning as an asynchronous word recognizer in the stand-alone mode.

When using the delay feature of the Model 10/Model 100A, several interesting and useful modes are possible. Table 4-1 describes what will be seen as the first word of the display for all four combinations of the POS/NEG time and CLOCK/TRIG delay switches. For positive time, the display is

Table 4-1

Delay Value Set To n ( $1 \leq n \leq 999$ )

| MODEL 100A<br>DISPLAY MODE | Model 10 Delay Select                                                                                    |                                                                                                                                   |

|----------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                            | CLOCK DELAY                                                                                              | TRIG DELAY                                                                                                                        |

| POSITIVE TIME              | First word of truth table is data at MUX output n clock pulses after the occurrence of the trigger word. | First word of truth table is data at MUX output after n+1 trigger occurrences. (Note trigger is <u>delayed</u> by n occurrences.) |

| NEGATIVE TIME              | First word of truth table is data at MUX output after (n-15) clock pulses.                               | First word of truth table is data at MUX output 15 clock pulses before n+1 trigger occurrences.                                   |

simply delayed for n clocks or triggers. (Note that analyzer triggering is delayed by the number of events set on the DELAY switches. Therefore, in the TRIG position, the analyzer actually displays after n+1 trigger occurrences.)

In the negative time mode, the interpretation is somewhat less obvious. For example, if the DELAY switch is set to "008" CLOCK delays, the first word of the truth table will be the output of the DISPLAY MUX a 8 minus 15 or -7 clock pulses relative to the trigger word. In other words, the seven data words preceding the trigger, the trigger itself, and the eight data words following the trigger will be displayed. This is a useful feature which allows viewing both pre- and post-triggering with a single data collection. In general, with the controls set for NEG TIME and TRIG DELAY, the display will show the 15 events preceding n+1 trigger occurrences and the trigger itself.

When triggering the Model 100A/Model 10 on unique addresses, the Model 100A trigger select switches are normally set to the "X" (don't care) position. When these switches are placed in the "1" and "0" positions, they can provide further qualification. This qualification on the output of the Model 10 multiplexer (Model 100A data inputs) occurs after all address qualification and delay requirements are satisfied. One easy way to visualize this is that in the POS TIME mode, the Model 100A trigger switches will place additional qualification on what will be the first word of the display. In the NEG TIME mode, the qualification occurs on what will be the last word of the display. When the display multiplexer switch is set to DATA, there will be a total of 24 bits  $\# Q_0$  which can specify the trigger: 16 address bits specified by the Model 10 ADDRESS switch and 8 data bits specified by the Model 100A trigger switches.

The open collector signal TRIGBUS+ is "wire-ANDed" to the Model 100A open collector trigger bus. Further "wire-AND" expansion of this bus is possible using the Model 10 trigger output BNC jack.

Reset switch S14 is in parallel with the Model 100A reset switch and has the same function. When the Model 10 is used as a stand-alone word recognizer, this reset switch can be used to arm the unit for a pending occurrence of the preset trigger word.

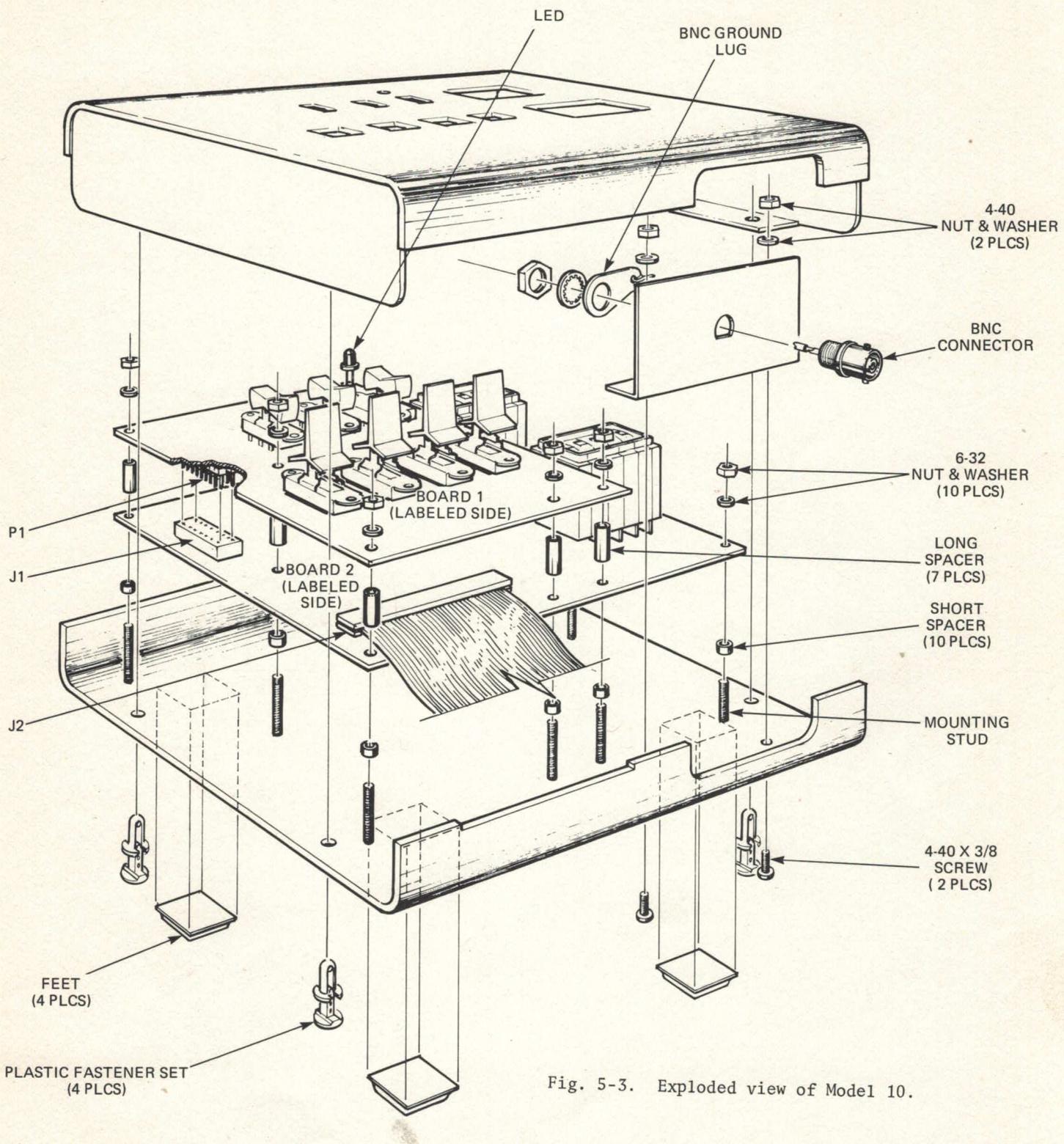

Although the Model 10 has two PC boards as compared to the single board in the Model 100A, it is actually easier to assemble. The reason is that there is no power supply to wire up, fewer switches to align, and only one BNC connector instead of four. The exploded view in Figure 5-3 illustrates these points.

It's important to note that all active components are tested before the kit leaves the factory. Therefore, you shouldn't have any difficulty getting the Model 10 to work properly as long as you carefully follow the step-by-step instructions in this section. In fact, it's a good idea to first familiarize yourself with all of the assembly steps and all of the parts of the Model 10 before you begin "getting it together."

The following is a list of recommended tools and some hints on their proper usage:

1. Low-power soldering station such as a Weller Model W-TCP, including moist sponge for wiping the tip: Use a small tip on the soldering iron and periodically clean it by wiping it on the moist sponge. When soldering, use 60/40 rosin core solder ONLY. Never, NEVER use acid core or externally applied fluxes. Also, never allow the tip to remain in contact with the PC board for more than 10 seconds. If you're not getting a shiny solder joint after applying the tip of the iron and the solder for a few seconds, then something must be wrong with the iron or solder you're using. (The Model 10 PC board is specially treated so that the solder should flow quickly and easily.)

2. Hex wrench: The easiest way to install the BNC connector is to use a  $\frac{1}{2}$ " hex wrench. If one is not available, use pliers--but be sure you're able to tighten the connector securely without damaging anything.

3. Small pair of wire cutters: Use these to trim the leads of all resistors, capacitors, and thumbwheel switches after soldering. It's not necessary to trim the leads of any of the IC sockets (except possibly J1).

4. Small pair of long nose pliers: Use these to carefully make the bends required to install the resistors and axial lead capacitors. (You can make this job a lot easier if you have one of those commonly available wedge-shaped, plastic lead bending tools.)

5. An inexpensive, 2X magnifying glass: This is a great way to inspect solder joints. Scan the board systematically and you'll be surprised what kind of potential problems even a low-cost, low-power, magnifying glass can uncover for you.

6. Patience: This is the most useful tool of all. If you take your time and inspect each step along the way, you'll save yourself a lot of grief later.

Misc. Assembly Hints - Before you begin, consider the following general hints which will assist you in performing the assembly of the PC boards:

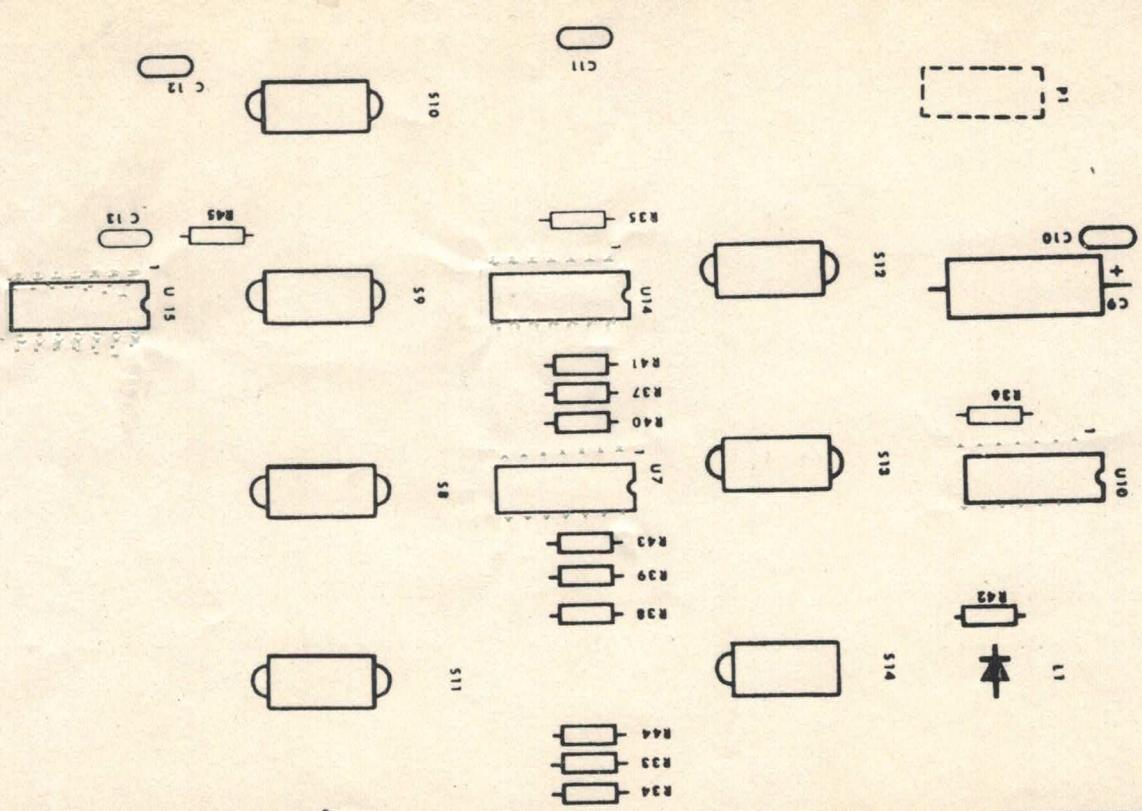

1. Use the Parts List to identify all components.

2. "Color in" components as you locate them in the assembly drawings of Figure 5-1 and 5-2.

3. Install all resistors so that the tolerance band is toward the right for all those that are horizontally-oriented; and facing toward the bottom of the board for all those that are vertically-oriented. This will help you to rapidly identify resistor values for later checkout and troubleshooting. (A resistor color-code chart is provided at the rear of the manual.)

4. Install all components of the same height at one time. Then lay a piece of cardboard or other flat material over the components to hold them in place as you turn the PC board over for soldering.

5. Never, NEVER use flux remover on the PC board after any of the rockers, paddles, or thumbwheel switches are installed. Even the vapor from the solvent can destroy the lubrication of the switches.

6. Note that one of the sockets supplied with the kit is a high-profile 16-pin DIP socket (J1). Make certain that this socket is mounted at the upper left-hand-corner of Board 2. (In some kits, this socket is a wire-wrap type, in others it has solder tails: either type is acceptable.)

7. Note also that the interconnecting plug (P1) for J1 has two different pin diameters: the pins coming out of one side are smaller in thickness than the pins on the opposite side. MAKE CERTAIN THAT THE LARGER DIAMETER PINS ARE INSERTED INTO THE UNDER SIDE OF BOARD 1 AS SHOWN IN FIGURE 5-3; OTHERWISE P1 WILL NOT MATE WITH J1.

The parts list for the Model 10 is shown next. If you find any discrepancies or damaged components prior to assembly, write to Paratronics, Inc. describing your problem so we can take the appropriate action.

Table 5-1

MODEL 10 PARTS LIST

## Board 1:

All resistors are  $\frac{1}{4}$ -watt, 5% tolerance:

|              |                                                                          |

|--------------|--------------------------------------------------------------------------|

| R33-R40, R44 | 4.7K ohm                                                                 |

| R41-43       | 1.0K ohm                                                                 |

| R45          | 470 ohm                                                                  |

| C13          | 15pf ceramic disc capacitor                                              |

| C9           | 47uf 15V electrolytic capacitor                                          |

| C10-C12      | .1uf 50V ceramic disc capacitor                                          |

| U14          | SN74LS132/9LS132 quad 2-input NAND schmidt trigger (15-volt inputs only) |

| U15          | SN74LS32/9LS32 quad 2-input OR gate (15-volt inputs only)                |

| U10          | SN74LS73 dual JK flip-flop                                               |

| U7           | SN74S15 Schottky triple 3-input AND gate with open collector outputs     |

| S8-S11       | 3-position double-throw paddle switch                                    |

| S12-S13      | double-pole-double-throw rocker switch                                   |

| S14          | double-pole-double-throw rocker switch with spring return                |

| L1           | LED HP5082-4860 or equivalent                                            |

| P1           | double-male 16-pin DIP plug                                              |

| Misc.        | PC board, four 14-pin IC sockets, mounting hardware                      |

## Board 2:

All resistors are  $\frac{1}{4}$ -watt, 5% tolerance:

|             |          |

|-------------|----------|

| R1-R16      | 4.7K ohm |

| R17-R28 R32 | 1.0K ohm |

| R29-R31     | 220 ohm  |

Board 2 continued

|                                  |                                                                                                                                                     |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| C1                               | 47 $\mu$ F 16V electrolytic capacitor                                                                                                               |

| C2-C8                            | .1 $\mu$ F 50V ceramic disc capacitor                                                                                                               |

| U1, U2, U8, U9                   | SN74LS367/9LS367 HEX three-state buffer<br>(15-volt inputs only)                                                                                    |

| U3, U4, U5, U6<br>SIGNETICS ONLY | SN74LS136/9LS136 quad EXCLUSIVE-OR gates<br>with open collector outputs (15-volt<br>inputs only)                                                    |

| U11, U12, U13                    | SN74LS160 or SN74LS162 decimal counters                                                                                                             |

| S1-S4                            | Hexadecimal (16-position) thumbwheel<br>switch with end plates                                                                                      |

| S5-S7                            | Decimal (10-position) thumbwheel switch<br>with end plates                                                                                          |

| J1                               | 16-pin high profile DIP socket for mating<br>with P1 on Board 1                                                                                     |

| J2                               | 50-pin flat ribbon header                                                                                                                           |

| Misc.                            | Flat ribbon and input probe assembly;<br>BNC connector; mounting hardware; four<br>14-pin sockets; seven 16-pin sockets;<br>case; hookup wire; etc. |

## ASSEMBLY INSTRUCTIONS

| STEP   | PROCEDURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | FIGURE |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|        | Steps 1-7 apply to the assembly of Board #1. This is the smaller of the two boards. Note that all components in the following steps (except the interconnecting DIP plug in step 7) are inserted from the labeled side.                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

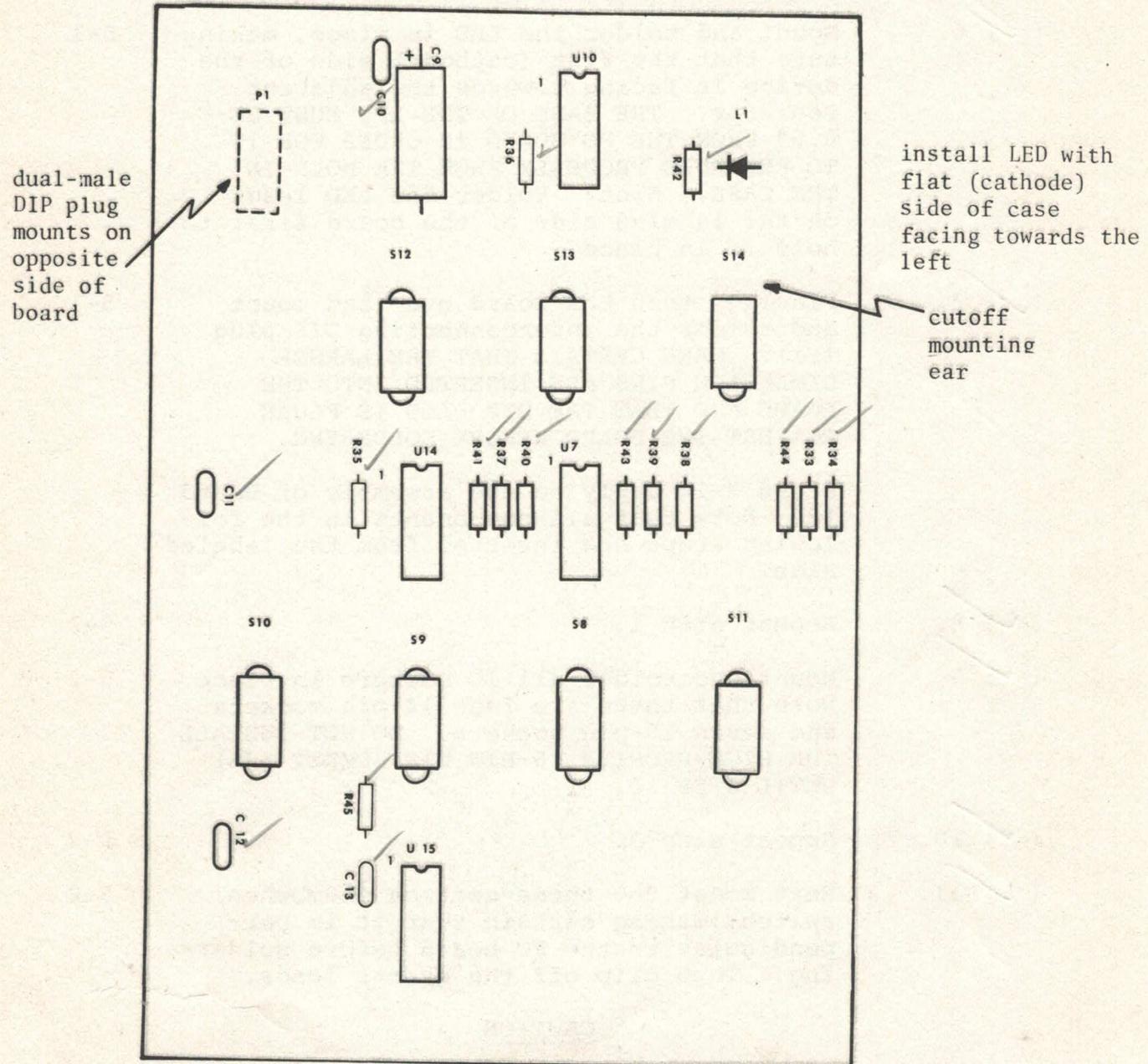

| (✓) 1. | Mount and solder all resistors in place. Before soldering, double-check to be sure that all resistors are properly located.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-1    |

| (✓) 2. | Mount and solder four 14-pin IC sockets in place.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-1    |

| (✓) 3. | Mount and solder the 0.1uF capacitors in place. Then mount the polarized 47uF capacitor, making certain that it is oriented properly.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-1    |

| (✓) 4. | Next, mount the two DPDT rocker switches S12 and S13. Then mount the DPDT spring return rocker switch, S14, MAKING SURE THAT THE CUTOFF MOUNTING EAR FACES TOWARDS RESISTOR R42 (near the top of the board).<br>NOTE: BEFORE SOLDERING IN PLACE, MAKE CERTAIN THAT THESE SWITCHES ARE SEATED ALL THE WAY DOWN AND ARE PERPENDICULAR TO THE PC BOARD; OTHERWISE, THE TOP OF THE CASE WILL NOT MATE PROPERLY. (Hint: Hold the board vertically as you solder the switches in place so that you can be sure that they are truly perpendicular. Then temporarily install the top cover and check that the cutouts permit free switch movement.) | 5-1    |

### CAUTION

DO NOT USE FLUX REMOVER IN STEPS 4 and 5: DAMAGE TO SWITCH LUBRICATION WILL RESULT.

MODEL 10 BOARD 1

Fig. 5-1. Model 10 Board #1 component layout.

| STEP    | PROCEDURE                                                                                                                                                                                                                                                                                                                                    | FIGURE |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| (✓) 5.  | Now mount the four paddle switches. Observe the note in step 4 before soldering in place.                                                                                                                                                                                                                                                    | 5-1    |

| (✓) 6.  | Mount and solder the LED in place, making sure that the flat (cathode) side of the device is facing towards the adjacent resistor. THE BASE OF THE LED MUST BE 0.9" FROM THE PC BOARD IN ORDER FOR IT TO PROTRUDE PROPERLY FROM THE HOLE IN THE CASE. Hint: Solder the LED leads on the labeled side of the board first to hold it in place. | 5-1    |

| (✓) 7.  | Finally, turn the board over and mount and solder the interconnecting DIP plug (P1). MAKE CERTAIN THAT THE LARGER DIMENSION PINS ARE INSERTED INTO THE BOARD AND THAT THE DIP PLUG IS FLUSH AGAINST THE BOARD BEFORE SOLDERING.                                                                                                              | 5-1    |

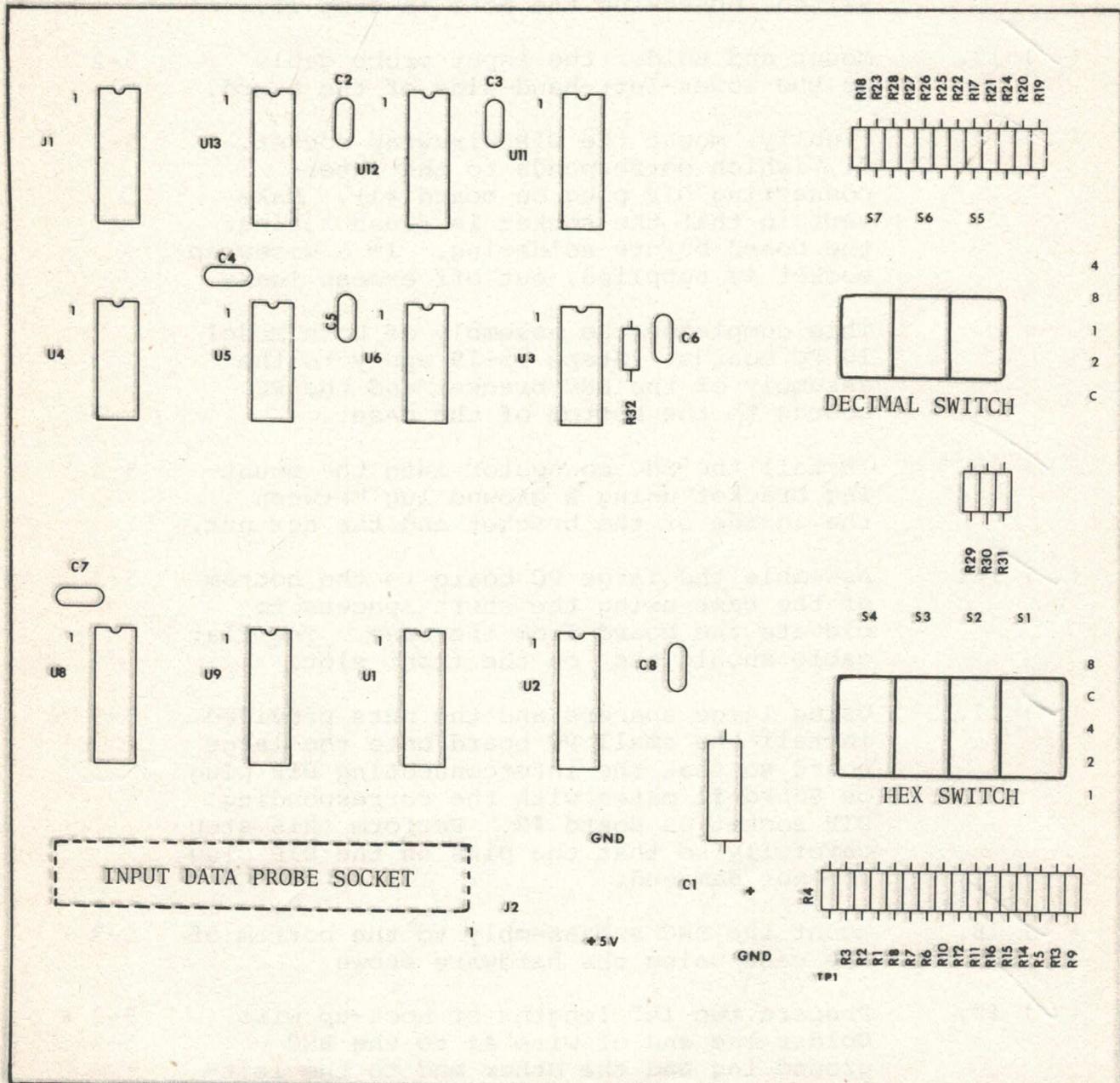

|         | Steps 8-14 apply to the assembly of Board #2. Note that all components in the following steps are inserted from the labeled side.                                                                                                                                                                                                            |        |

| (✓) 8.  | Repeat step 1.                                                                                                                                                                                                                                                                                                                               | 5-2    |

| (✓) 9.  | Mount and solder all IC sockets in place. Note that there are four 14-pin sockets and seven 16-pin sockets. DO NOT INSTALL THE HIGH-PROFILE 16-PIN DIP SOCKET (J1) UNTIL STEP 14.                                                                                                                                                            | 5-2    |

| (✓) 10. | Repeat step 3.                                                                                                                                                                                                                                                                                                                               | 5-2    |

| (✓) 11. | Next mount the three-section thumbwheel switch, making certain that it is perpendicular to the PC board before soldering. Then clip off the excess leads.                                                                                                                                                                                    | 5-2    |

#### CAUTION

DO NOT USE FLUX REMOVER IN STEPS 11 and 12.

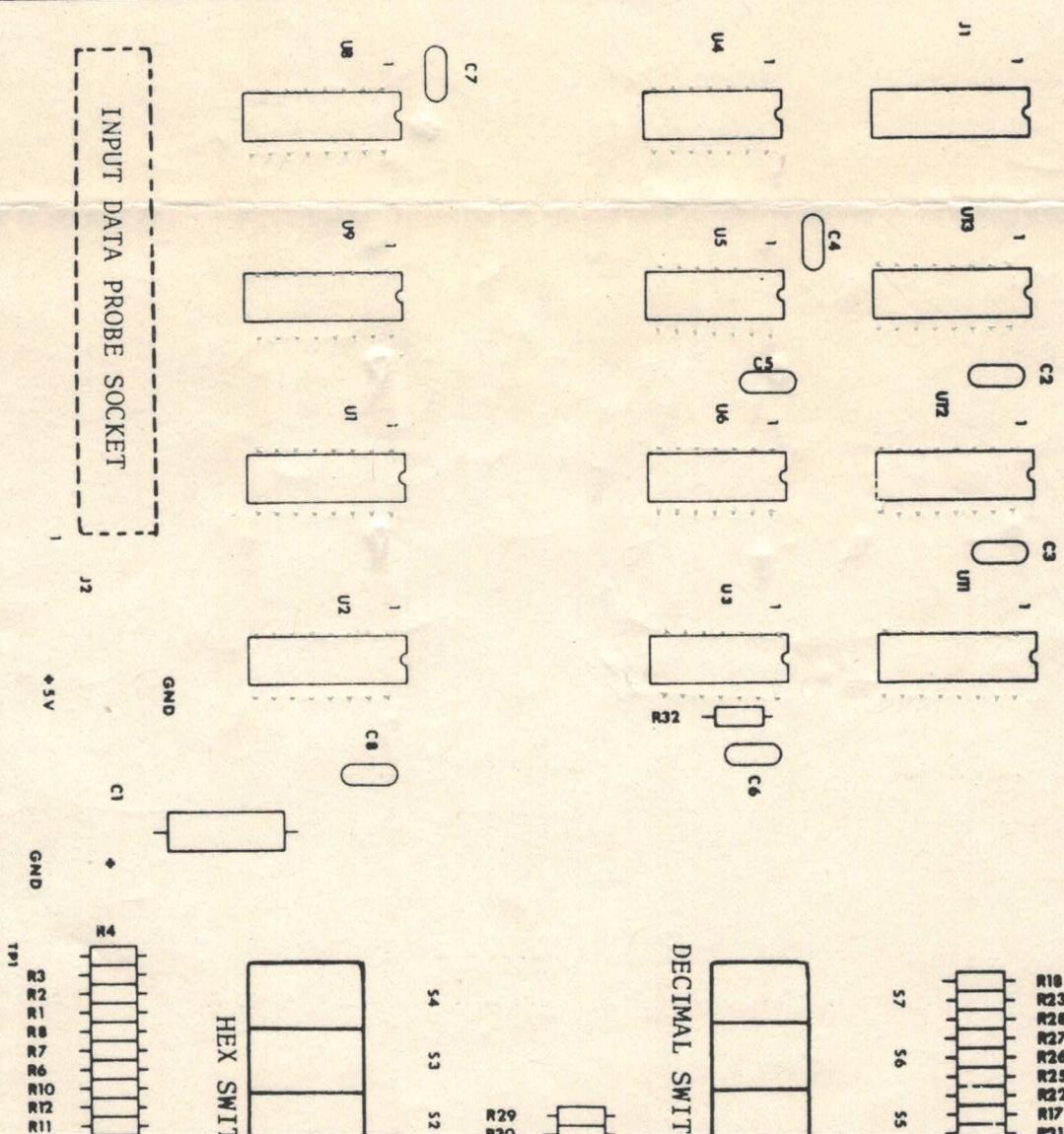

MODEL 10 BOARD 2

Fig. 5-2. Model 10 Board #2 component layout.

| STEP    | PROCEDURE                                                                                                                                                                                                                                                                                                                                                 | FIGURE    |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| (✓) 12. | Now mount the four-section thumbwheel switch, observing the note in step 11.                                                                                                                                                                                                                                                                              | 5-2       |

| (✓) 13. | Mount and solder the input probe cable at the lower-left-hand-side of the board.                                                                                                                                                                                                                                                                          | 5-2       |

| (✓) 14. | Finally, mount the DIP wirewrap socket, J1, (which corresponds to the inter-connecting DIP plug on board #1). Make certain that the socket is flush against the board before soldering. If a wirewrap socket is supplied, cut off excess leads.                                                                                                           | 5-2       |

|         | This completes the assembly of both Model 10 PC boards. Steps 15-19 apply to the assembly of the BNC bracket and the PC boards to the bottom of the case.                                                                                                                                                                                                 |           |

| (✓) 15. | Install the BNC connector into the mounting bracket using a ground lug between the inside of the bracket and the hex nut.                                                                                                                                                                                                                                 | 5-3       |

| (✓) 16. | Assemble the large PC board to the bottom of the case using the short spacers to elevate the board from the case. The flat cable should rest on the front slot.                                                                                                                                                                                           | 5-3       |

| (✓) 17. | Using large spacers and the nuts provided, install the small PC board onto the large board so that the interconnecting DIP plug on Board #1 mates with the corresponding DIP socket on Board #2. Perform this step carefully so that the pins on the DIP plug are not damaged.                                                                            | 5-3       |

| (✓) 18. | Mount the BNC subassembly to the bottom of the case using the hardware shown.                                                                                                                                                                                                                                                                             | 5-3       |

| (✓) 19. | Prepare two 1½" lengths of hook-up wire. Solder one end of wire #1 to the BNC ground lug and the other end to the <u>left-hand</u> pad on Board #2, above the <u>Paratronics, Inc.</u> label. Solder one end of wire #2 to the solder post on the BNC connector, and the other end to the <u>right-hand</u> pad above the <u>Paratronics, Inc.</u> label. | 5-2 & 5-3 |

Fig. 5-3. Exploded view of Model 10.

## STEP

## PROCEDURE

## FIGURE

(✓) 20.

Install all IC's, making absolutely sure that they are located and oriented properly; otherwise, they may be damaged when power is later applied.

Your Model 10 is now ready for checkout. Please go to the next section before installing the top cover. NOTE: FOR TROUBLE-SHOOTING PURPOSES, THE PC BOARDS CAN BE REMOVED FROM THE BOTTOM OF THE CASE AS A UNIT. TO DO THIS, CAREFULLY UNSOLDER THE TWO BNC LEADS AT THE BNC CONNECTOR. THEN LIFT THE TWO BOARDS TOGETHER FROM THE THREADED CASE POSTS. HINT: INSERT FIVE #6 SCREWS (1½" long) IN THE MOUNTING HOLES TO HOLD THE LONG SPACERS AND THE TWO BOARDS TOGETHER. TIGHTEN DOWN WITH #6 HEX NUTS. (IF IT BECOMES NECESSARY TO SEPARATE THE BOARDS, A 16-PIN FLAT RIBBON ADAPTOR CABLE WILL BE REQUIRED TO INTERCONNECT THE TWO BOARDS.)

(✓) 21.

After satisfactory checkout, install the top cover to the bottom of the case using the four plastic fastener sets. If the optional baseplate is used, the fasteners must be inserted into the baseplate first. NOTE: IF IT IS NOTICED THAT THE SWITCHES DO NOT LINE UP WITH THE MOUNTING HOLES, IT WILL BE NECESSARY TO LOOSEN THE PC BOARD NUTS AND SLIDE THE BOARDS AROUND SLIGHTLY. IF THIS DOESN'T WORK, THEN YOU MUST REMOVE ONE OR BOTH PC BOARDS FROM THE BOTTOM OF THE CASE AND DESOLDER, ADJUST, AND RESOLDER THE MISALIGNED SWITCH.

5-3

(✓) 22.

Install the four press-on feet to the bottom of the case. If the optional baseplate is used, mount the Model 10 to the baseplate first and then use the feet cut-outs as a guide.

5-3

\* \* \*

THIS COMPLETES THE ASSEMBLY OF THE MODEL 10

## 6.0

CHECKING IT OUT

The Model 10 can be checked out either with the Model 100A or with an auxiliary +5V  $\pm 5\%$  (300 ma) power supply. For operation and checkout with the Model 100A, the 16-pin DIP plug portion of the flat cable assembly of the Model 10 should be inserted into the Model 100A input socket. This requires removal of the Model 100A top cover by pulling out FOUR plastic fasteners (two on each side). The original input probe plug and cable of the Model 100A are not used.

For operation and checkout without the Model 100A, +5V should be CAREFULLY applied to pin 9 of the 16-pin DIP plug and ground at pin 16.

## 6.1

PRELIMINARY CHECKOUT

Leave all input probes of the Model 10 unconnected. Set the controls of the Model 10 as follows:

| Control            | Setting                  |

|--------------------|--------------------------|

| $Q_0$              | "X"                      |

| Address select     | "FFFF"                   |

| All other switches | (settings not important) |

Now monitor pin 6 of U7 with a logic probe, scope or voltmeter. It should be a logic 1 (at approximately +5V) indicating that the address comparator has a "match." (Floating address inputs are treated as logic 1's.) For all other address switch settings, or if the  $Q_0$  qualifier is switched to the "0" position, pin 6 of U7 should be at the logic 0 (0.4V) state.

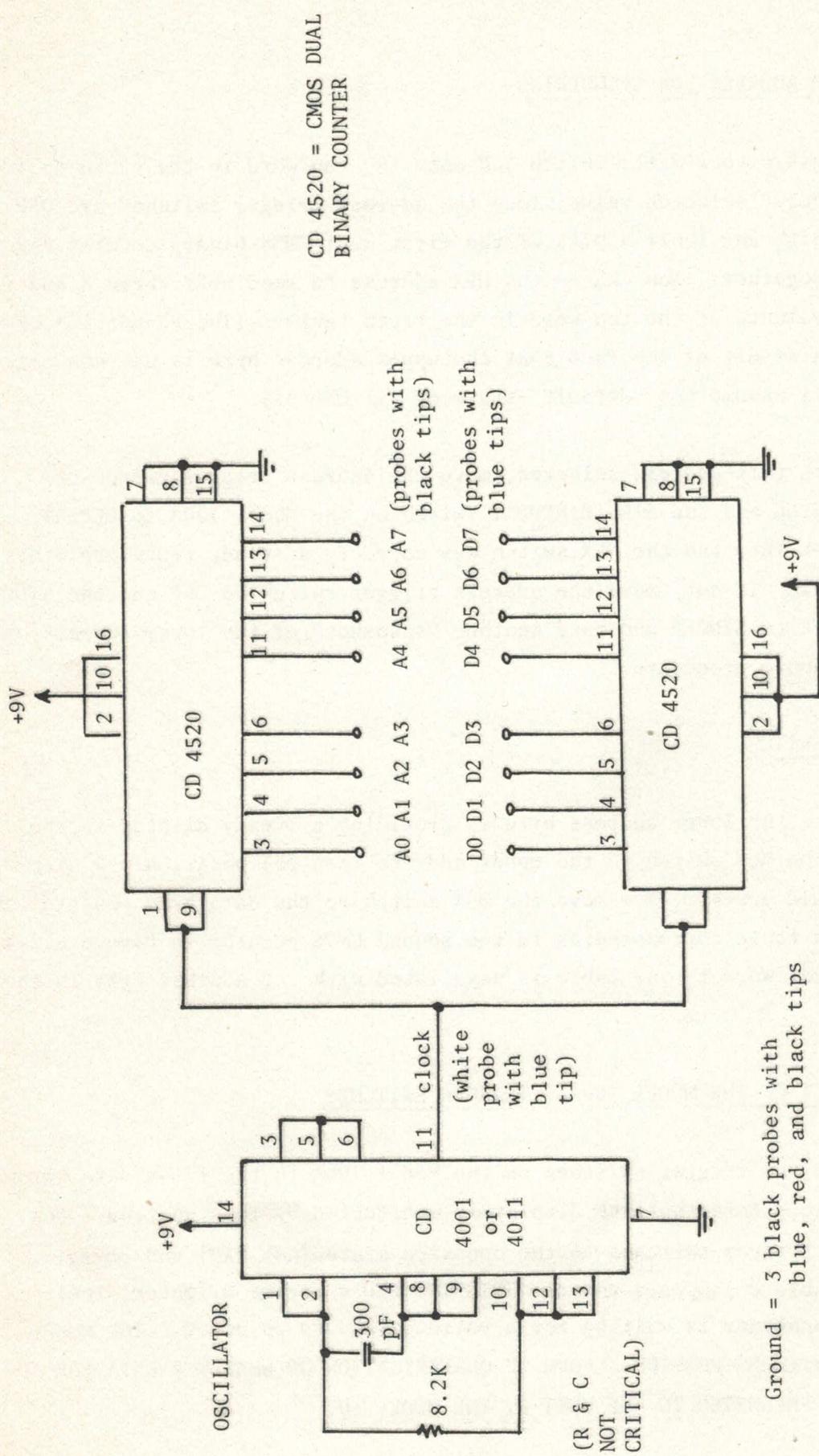

Connect the Model 100A HOR, VERT, and BLANK outputs to an oscilloscope for display. The test circuit in Figure 6.2-1 or a similar one which cycles at least 16 bits should be used.

INITIAL SET-UP

Connect address inputs A0 through A7 and data inputs D0 through D7 to the test circuit. (Leave A8 through A15 unconnected at this time.) Connect the clock input to the test circuit clock. Set the controls on the Model 100A and Model 10 as follows:

| Model 100A Control Settings |                |

|-----------------------------|----------------|

| Display format              | HEX            |

| Clock edge                  | negative-going |

| Display mode                | POS TIME       |

| SINGLE/REPEAT               | SINGLE         |

| D0-D7                       | ALL "X"        |

| Model 10 Control Settings                  |                |

|--------------------------------------------|----------------|

| Clock edge                                 | positive-going |

| Delay select                               | CLOCK          |

| DELAY                                      | "000"          |

| Address trigger                            | OFF            |

| Q <sub>0</sub> , Q <sub>1</sub> qualifiers | "X"            |

| ADDRESS                                    | "FF00"         |

| Display MUX                                | LO ADDR        |

Fig. 6.2-1. Simple CMOS counter circuit for checking out the Model 10.

### OBTAINING A VALID ADDRESS FOR TRIGGERING

Press either RESET switch and note the top word in the truth table, which is a "randomly" selected value since the address trigger switches are OFF and the upper 4 bits and lower 4 bits of the first dual CMOS binary counter may not be counting together. Now change the HEX address to read FFXY where X and Y are the HEX equivalents of the top word in the truth table. (The FF portion of this address is a result of the fact that the upper address byte is not connected and therefore will assume the "default" state of all ONE's.)

With this address selected, move the address trigger switch on the Model 10 to SYNC and the SINGLE/REPEAT switch on the Model 100A to REPEAT. If the address set into the the HEX switch was correct, a steady truth table display should appear. If not, move the address trigger switch to OFF and the SINGLE/REPEAT switch back to SINGLE and take another "snapshot" of the lower address byte. Then repeat the above procedure.

### TESTING THE MUX SWITCH

Once the lower address byte is providing a steady display in the SYNC mode, move the MUX switch to the upper address (center) position: a display of all ONE's should appear. Now move the MUX switch to the data byte position and observe the truth table corresponding to the second CMOS counter in Figure 6.2-1. Note that the first word in the table is associated with the address FFXY in the HEX switch.

### TESTING THE AFFECT OF THE MODEL 100A'S TRIGGER SWITCHES

Set the trigger switches on the Model 100A to the first data word in the truth table. Note that the display is unaffected by this setting. Now move one or more trigger switches to the opposite state (not "X") and observe that the truth table disappears and the TRIG IND LED's become brighter, indicating that the analyzer is waiting for a valid data word to occur. THE MODEL 100A'S TRIGGER SWITCHES PROVIDE A FORM OF QUALIFICATION ON WHATEVER DATA (OR ADDRESS BYTES) ARE PRESENTED TO THE UNIT BY THE MODEL 10.

### TESTING THE DELAY

Before proceeding, check to be sure that the CLOCK/TRIG switch on the Model 10 is set to CLOCK. Then return all trigger switches on the Model 100A to "X." The truth table for the data should again appear steady on the CRT. Now, switch the Model 100A to the SINGLE mode to store the display and set the trigger switches to the third data byte in the truth table, counting from the top. Press either RESET switch and observe that the truth table disappears. Next, set the delay switch to 002 and observe that the truth table reappears, with the third data byte now at the top of the table. Move the delay to 003, press RESET, and note that the analyzer does not trigger. This exercise illustrates how the delay feature of the Model 10 and the trigger switches of the Model 100A can be used to trigger on a data word occurring up to 1000 clock pulses after the address word.

Move all of the trigger switches on the Model 100A back to "X," and the SINGLE/REPEAT switch back to REPEAT. Then set the delay to 000 and the MUX switch to the lower address byte position and a steady truth table should appear as before. Now increment the delay by one integer at a time and note that the entire table shifts up towards the top of the screen as the delay is increased. When 015 is set into the delay, the word that was at the bottom of the table with a delay setting of 000 will now appear at the top.

Now set the delay back to 000 and change the POS/NEG TIME switch on the Model 100A to NEG. Note that the lower address byte, which previously appeared at the top of the truth table, is now at the bottom. Next, increment the delay in integer steps and watch this word move towards the top of the display. When 015 is reached, the lower address byte set into the HEX switch should appear at the top of the screen.

### TESTING THE UPPER ADDRESS BYTE

Interchange the probes corresponding to the lower address byte (black tips) and the upper address byte (red tips) and change the HEX address

switch to XYFF. Then repeat the above steps.

#### TESTING THE TRIG FEATURE

Set the delay switch back to 000 and switch the CLOCK/TRIG switch to TRIG. Now, increment the "hundreds" position of the delay switch, i.e., 100, 200, 300, etc. As this setting is increased, the number of input trigger words which must occur before a truth table will be displayed increases one-hundred-fold per step. Depending on the clock frequency of the test circuit oscillator, the display should begin to flicker as the delay is increased since greater intervals of time must pass before each truth table is permitted to occur.

#### TESTING THE QUALIFIER

The qualifiers  $Q_0$  and  $Q_1$  can now be statically checked out with a simple test. With both  $Q_0$  and  $Q_1$  input probes left open, the Model 100A/Model 10 should trigger with the qualifiers in the "1" or "X" positions and not trigger when either is to "0."

Now repeat the test with both qualifier inputs grounded. The analyzer should trigger in the "0" or "X" positions, but not trigger if either qualifier is set to "1."

6.3

#### CHECKING OUT THE MODEL 10 AS A STAND-ALONE WORD RECOGNIZER

In order to check out the Model 10 as a stand-alone word recognizer, the TRIG output should be viewed with an oscilloscope which should be triggered independently from the circuit under test. For example, the falling edge of the most significant bit of the test circuit should be used to trigger the scope by connecting the MSB to the external trigger input of the scope. The word recognizer should be connected to the test circuit as described in Section 6.2 above. Now, the relative timing of the output pulse with respect to the counter MSB can be observed as different delay values and address values are set into the word recognizer. This exercise illustrates how the Model 10 can add digitally delayed sweep capability to an ordinary scope.

If any difficulty in checkout is encountered, refer to Section 7.0 for troubleshooting guidelines. If everything checks out, install the top cover using the four plastic fasteners as described in Section 5.0, assembly step 21.

## 7.0

WHAT IF IT DOESN'T WORK RIGHT?

Although all active components of each Model 10 kit are thoroughly tested at the factory, it's still possible that one will fail during or shortly after assembly. However, as shown in Figure 7-1, the circuit is straightforward and relatively easy to troubleshoot; but if you can't find the problem, we'll do everything we can to help.

## 7.1

CHECKING YOUR WORK

A large majority of problems associated with kit-building can be traced to minor errors in assembly. The following checklist will help you find most assembly-related problems:

1. Check to make certain that all IC's are located correctly and oriented with pin 1 in the proper position. If an IC has been installed backwards and power is applied, it will probably overheat and be destroyed. See Figures 5-1 and 5-3.

2. Check all resistors to make sure they are the proper value and in the proper position.

3. Make sure all capacitors are installed correctly. Check the polarity of the two electrolytic types.

4. Inspect all solder joints. A low-power (2X) magnifying glass is useful here. Check to make sure all connections are shiny and that there are no solder bridges shorting to adjacent pads.

5. Make certain that P1 on Board 1 and J1 on Board 2 mate correctly.

NOTE: 1. ALL RESISTORS ARE 1/4W, 5%.

| REF DES | MFR | TYPE   | NO. | +5 V | GND |

|---------|-----|--------|-----|------|-----|

| U7      |     | 74S15  |     | 14   | 7   |

| U10     |     | 74LS13 |     | 4    | 11  |

| U14     |     | 74LS12 |     | 14   | 7   |

| U15     |     | 74LS32 |     | 14   | 7   |

Copyright 1977

|                    |                      |                                |   |

|--------------------|----------------------|--------------------------------|---|

| CONTRACT NO. _____ |                      | PARATRONICS, INC.              |   |

| APPO _____         |                      | 800 Charcot Ave                |   |

| DATE _____         |                      | San Jose, Ca 95131             |   |

| DIR                | Mr. John H. H. _____ | 5                              | 1 |

| CHK                | Mr. John H. H. _____ | 10/17/72                       | 1 |

| STRU               | Mr. John H. H. _____ |                                | 1 |

| MATL               | Mr. John H. H. _____ |                                | 1 |

| T.C                | Mr. John H. H. _____ |                                | 1 |

| PNG                | Mr. John H. H. _____ |                                | 1 |

| ENGR               | Mr. John H. H. _____ |                                | 1 |

| ENGR               | Mr. John H. H. _____ |                                | 1 |

| MODEL 10 BOARD 1   |                      | SIZE CODE (ENT. NO. 100-10172) |   |

| APPO _____         |                      | 100-10172                      | 1 |

| DATE _____         |                      | 100-10172                      | 1 |

| DIR                |                      | 100-10172                      | 1 |

| CHK                |                      | 100-10172                      | 1 |

| STRU               |                      | 100-10172                      | 1 |

| MATL               |                      | 100-10172                      | 1 |

| T.C                |                      | 100-10172                      | 1 |

| PNG                |                      | 100-10172                      | 1 |

| ENGR               |                      | 100-10172                      | 1 |

| ENGR               |                      | 100-10172                      | 1 |

| SCALE              |                      | 100-10172                      | 1 |

| SHEET              |                      | 100-10172                      | 1 |

| C                  |                      | 100-10172                      | 1 |

| CR                 |                      | 100-10172                      | 1 |

Fig. 7-1a. Model 10 Board 1.

Fig. 7-1b. Model 10 Board 2.

TABLE 7-1

## MODEL 10 TRIGGER EXPANDER TROUBLESHOOTING CHART

| SYMPTOM                                    | PROBABLE CAUSE                                                                                               | REMEDY                                                                                                                                                                                                       |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|