IBM Confidential Restricted. DO NOT COPY

IBM CONFIDENTIAL-RESTRICTED

DO NOT COPY

FUNCTIONAL SPECIFICATION

December 1, 1983

E.C.# A07313

P.N. 6080439

IBM Confidential Restricted. DO NOT COPY

IBM CONFIDENTIAL-RESTRICTED

DO NOT COPY

FUNCTIONAL SPECIFICATION

December 1, 1983

E.C.# A07313

P.N. 6080439

IBM Confidential Restricted. DO NOT COPY

ROMP Functional Specification

December 1, 1983

This document contains information of a proprietary nature and is classified IBM CONFIDENTIAL-RESTRICTED and may not be reproduced. No information contained herein shall be divulged to persons other than IBM employees authorized by the nature of their duties to receive such information.

Copy \_\_\_\_\_ Assigned to \_\_\_\_\_

I certify that the attached document has been disposed of by established IBM Confidential security procedures.

Signature \_\_\_\_\_ Date \_\_\_\_\_

When you receive an updated level of this document, you are required to return only this cover page to the address shown below.

Tom Whiteside

F61/045

Austin, Tx

T.L. 678-9791

Document Printed July 25, 1984

**COPY** \_\_\_\_\_

**ROMP Functional Specification**

**Document Number 6080439**

**December 1, 1983**

**Tom Whiteside**

**IBM Entry Systems Division

Dept. F61 Bldg. 045

11400 Burnet Road

Austin, TX 78758

Tie Line 678-9232**

**IBM Confidential Restricted. DO NOT COPY**

0

**COPY** \_\_\_\_\_

**ROMP Functional Specification**

**Document Number 6080439**

**December 1, 1983**

**Tom Whiteside**

**IBM Entry Systems Division

Dept. F61 Bldg. 045

11400 Burnet Road

Austin, TX 78758

Tie Line 678-9232**

**IBM Confidential Restricted. DO NOT COPY**

CONTENTS

|         |                                                |    |

|---------|------------------------------------------------|----|

| 1.0     | Introduction                                   | 1  |

| 1.1     | Document Overview                              | 1  |

| 1.2     | ROMP Objectives                                | 1  |

| 1.3     | ROMP Processor Highlights                      | 1  |

| 1.4     | Programming Support Overview                   | 3  |

| 1.5     | Hardware Documentation Overview                | 3  |

| 1.6     | Signal Naming Conventions                      | 4  |

| 2.0     | System Organization And Control                | 5  |

| 2.1     | Main Storage                                   | 5  |

| 2.2     | Storage Channel                                | 7  |

| 2.3     | Programmed I/O                                 | 7  |

| 2.4     | Processor                                      | 7  |

| 2.5     | Processor States                               | 7  |

| 2.5.1   | Executing, Wait, Check Stop, and Stopped State | 7  |

| 2.5.2   | Problem and Supervisor States                  | 8  |

| 2.6     | General-Purpose Registers                      | 9  |

| 2.7     | System Control Registers                       | 9  |

| 2.7.1   | Counter Source, Counter, and Timer Status      | 12 |

| 2.7.2   | Multiplier Quotient                            | 12 |

| 2.7.3   | Machine Check Status and Program Check Status  | 12 |

| 2.7.4   | Interrupt Request Buffer                       | 12 |

| 2.7.5   | Instruction Address Register                   | 12 |

| 2.7.6   | Interrupt Control Status                       | 13 |

| 2.7.7   | Condition Status                               | 13 |

| 2.8     | System Timer Facility                          | 14 |

| 2.8.1   | Counter                                        | 15 |

| 2.8.2   | Counter Source                                 | 15 |

| 2.8.3   | Timer Status                                   | 15 |

| 2.8.4   | Programming Note: System Timer Operation       | 16 |

| 2.9     | Interrupts                                     | 17 |

| 2.9.1   | Processor Priority                             | 18 |

| 2.9.1.1 | Interrupt Request Priority                     | 19 |

| 2.9.1.2 | Interrupt Priority Assignment                  | 19 |

| 2.9.2   | Point of Interrupt                             | 19 |

| 2.9.3   | Error Handling                                 | 19 |

| 2.9.4   | Program Status                                 | 20 |

| 2.9.4.1 | Old/New Program Status Pairs                   | 20 |

| 2.9.4.2 | Location of Old/New Program Status Pairs       | 20 |

| 2.9.5   | System Control Registers                       | 20 |

| 2.9.5.1 | Interrupt Request Buffer                       | 21 |

| 2.9.5.2 | Interrupt Control Status                       | 21 |

| 2.9.6   | Occurrence of Interrupts                       | 22 |

| 2.9.7   | Programming Note: Interrupt Facility           | 22 |

| 2.9.8   | Programming Notes: Interrupt Servicing         | 23 |

| 3.0     | Instruction Set                                | 26 |

| 3.1     | General Description                            | 26 |

| 3.2     | Storage Access                                 | 30 |

| 3.2.1   | Load Instructions                              | 31 |

|                                                        |    |

|--------------------------------------------------------|----|

| 3.2.2 Test and Set Instruction . . . . .               | 34 |

| 3.2.3 Store Instructions . . . . .                     | 34 |

| 3.3 Address Computation . . . . .                      | 37 |

| 3.4 Branching . . . . .                                | 40 |

| 3.4.1 Branch And Link Instructions . . . . .           | 42 |

| 3.4.2 Conditional Branches . . . . .                   | 44 |

| 3.5 Traps . . . . .                                    | 49 |

| 3.6 Moves and Inserts . . . . .                        | 51 |

| 3.6.1 Move Character Instructions . . . . .            | 51 |

| 3.6.2 Move To And From Test Bit Instructions . . . . . | 53 |

| 3.7 Arithmetic . . . . .                               | 56 |

| 3.7.1 Add Instructions . . . . .                       | 57 |

| 3.7.2 Absolute Instruction . . . . .                   | 59 |

| 3.7.3 Complement Instructions . . . . .                | 59 |

| 3.7.4 Compare Instructions . . . . .                   | 60 |

| 3.7.5 Extend Sign Instruction . . . . .                | 62 |

| 3.7.6 Subtract Instructions . . . . .                  | 63 |

| 3.7.7 Divide And Multiply Step Instructions . . . . .  | 65 |

| 3.8 Logical Operations . . . . .                       | 69 |

| 3.8.1 Clear And Set Bit Instructions . . . . .         | 69 |

| 3.8.2 AND Instructions . . . . .                       | 71 |

| 3.8.3 OR Instructions . . . . .                        | 72 |

| 3.8.4 Exclusive OR Instructions . . . . .              | 73 |

| 3.8.5 Count Leading Zeroes Instruction . . . . .       | 75 |

| 3.9 Shifts . . . . .                                   | 76 |

| 3.9.1 Shift Algebraic Right Instructions . . . . .     | 76 |

| 3.9.2 Shift Right Instructions . . . . .               | 77 |

| 3.9.3 Shift Left Instructions . . . . .                | 80 |

| 3.10 System Control . . . . .                          | 83 |

| 3.10.1 Move To And From SCR Instructions . . . . .     | 83 |

| 3.10.2 Clear And Set SCR Bit Instructions . . . . .    | 84 |

| 3.10.3 Load Program Status Instruction . . . . .       | 85 |

| 3.10.4 Wait Instruction . . . . .                      | 86 |

| 3.10.5 Supervisor Call Instruction . . . . .           | 87 |

| 3.11 Input/Output . . . . .                            | 88 |

| 4.0 INPUT/OUTPUT Facility . . . . .                    | 90 |

| 4.1 I/O Capability . . . . .                           | 90 |

| 4.1.1 Programmed I/O . . . . .                         | 90 |

| 4.1.2 Privileged I/O Device Connection . . . . .       | 90 |

| 4.1.3 I/O Interrupt Requests . . . . .                 | 91 |

| 5.0 ROMP Storage Channel . . . . .                     | 92 |

| 5.1 General Description . . . . .                      | 92 |

| 5.2 Storage Channel Definition . . . . .               | 95 |

| 5.2.1 Address And Data Bus . . . . .                   | 95 |

| 5.2.2 Tag Bus . . . . .                                | 95 |

| 5.2.3 Control Signals . . . . .                        | 95 |

| 5.2.4 Address Extension Bus . . . . .                  | 96 |

| 5.2.5 RSC Clocks . . . . .                             | 96 |

| 5.3 RSC Signal Definitions . . . . .                   | 97 |

| 5.3.1 Address/Data Bus Definition . . . . .            | 97 |

| 5.3.2 Tag Bus Definition . . . . .                     | 98 |

| 5.3.3 Address Extension Bus Definition . . . . .       | 99 |

|                                                                                |     |

|--------------------------------------------------------------------------------|-----|

| 5.3.4 Storage Channel Clocking . . . . .                                       | 100 |

| 5.4 Bus Operation . . . . .                                                    | 101 |

| 5.4.1 Data Alignment . . . . .                                                 | 101 |

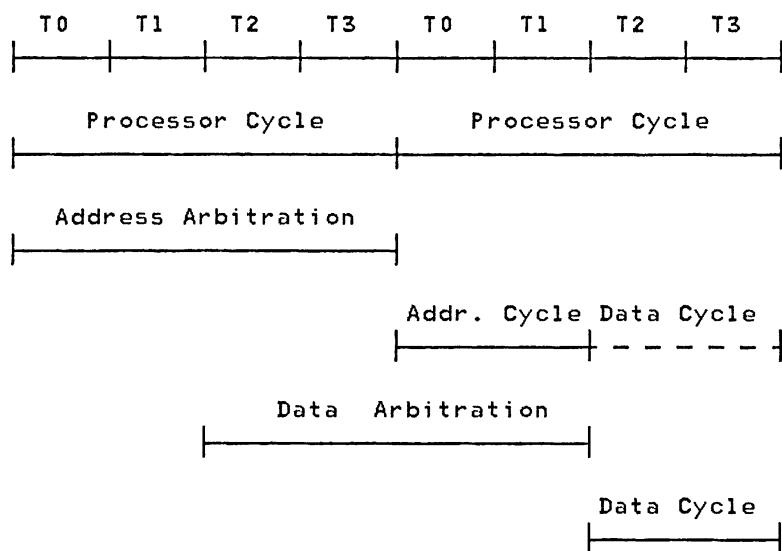

| 5.4.2 Bus Arbitration . . . . .                                                | 102 |

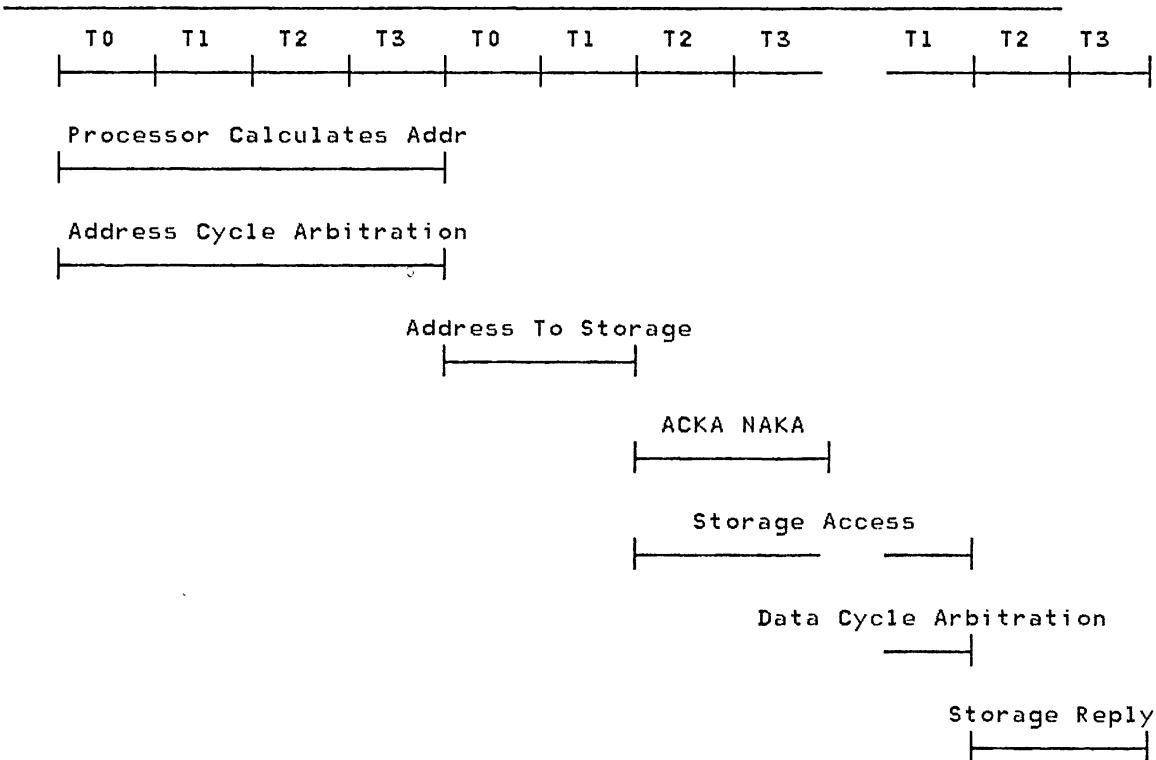

| 5.4.3 Read Request . . . . .                                                   | 103 |

| 5.4.4 Write Request . . . . .                                                  | 105 |

| 5.4.5 Error Handling . . . . .                                                 | 106 |

| 5.4.6 Idle Mode . . . . .                                                      | 107 |

| 5.4.7 Reset . . . . .                                                          | 107 |

| 5.4.8 Illegal ACKD/NAKD Responses . . . . .                                    | 107 |

| 5.4.9 Engineering Note: ROMP Response To Illegal ACKD/NAKD Responses . . . . . | 108 |

| 5.4.10 Hold Time-Out Counter . . . . .                                         | 108 |

| 5.4.11 Storage Protection and Address Translation . .                          | 109 |

| 5.5 Storage Channel I/O Pin Summary . . . . .                                  | 110 |

| 5.5.1 Storage Channel I/O Pin Summary for Processor                            | 110 |

| 5.5.2 Storage Channel Pin Summary for a Typical RSC Component . . . . .        | 111 |

| 5.6 ROMP Storage Channel Timing Relationships . . . . .                        | 111 |

| 6.0 Initialization . . . . .                                                   | 117 |

| 6.1 Power-on Reset . . . . .                                                   | 117 |

| 6.1.1 Processor and System Reset . . . . .                                     | 117 |

| 6.1.2 Register Initialization And Diagnostics . . .                            | 118 |

| 6.1.3 Fail Pin State . . . . .                                                 | 118 |

| 6.2 Program Initialization . . . . .                                           | 118 |

| 6.2.1 Initial Program Load . . . . .                                           | 119 |

| 6.2.2 IAR Load . . . . .                                                       | 119 |

| 6.2.3 Engineering Notes: Initialization . . . . .                              | 119 |

| 7.0 Reliability, Availability, and Serviceability . .                          | 121 |

| 7.1 RAS Facilities . . . . .                                                   | 121 |

| 7.2 System Error Detection and Reporting . . . . .                             | 121 |

| 7.2.1 Internal Diagnostics . . . . .                                           | 121 |

| 7.2.2 Machine-Check Errors . . . . .                                           | 121 |

| 7.2.2.1 Machine-Check Error Handling . . . . .                                 | 122 |

| 7.2.2.2 Machine-Check Status . . . . .                                         | 122 |

| 7.2.3 Engineering Note: RSC Retry . . . . .                                    | 123 |

| 7.2.4 Program-Check Errors . . . . .                                           | 124 |

| 7.2.4.1 Program-Check Error Handling . . . . .                                 | 124 |

| 7.2.4.2 Program-Check Status . . . . .                                         | 125 |

| 7.2.4.3 Programming Note: Instruction Restart . .                              | 126 |

| 7.2.5 Simultaneous Program Check and Machine Check Errors . . . . .            | 128 |

| 7.3 Multiple Occurrence of Errors . . . . .                                    | 129 |

| 8.0 Multiprocessor System . . . . .                                            | 130 |

| 8.1 General Description . . . . .                                              | 130 |

| 8.2 Test & Set Instruction Operation . . . . .                                 | 130 |

| 8.3 Multiprocessor System Interconnection . . . . .                            | 130 |

| 9.0 Storage Controller Functions . . . . .                                     | 134 |

| 9.1 Storage Protect and Address Translation Overview                           | 136 |

| 9.2 Storage Protect . . . . .                                                  | 137 |

|                                                        |     |

|--------------------------------------------------------|-----|

| 9.3 Address Translation . . . . .                      | 140 |

| 10.0 Processor Support Functions . . . . .             | 142 |

| 10.1 Front Panel Support . . . . .                     | 142 |

| 10.2 Support Processor Facilities . . . . .            | 142 |

| 11.0 Performance . . . . .                             | 144 |

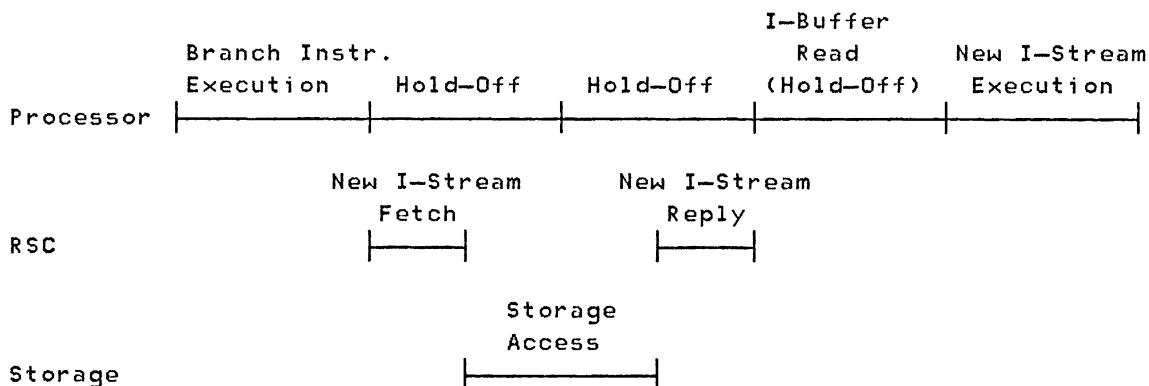

| 11.1 Branch Hold-off . . . . .                         | 144 |

| 11.2 Branch and Execute Hold-off . . . . .             | 146 |

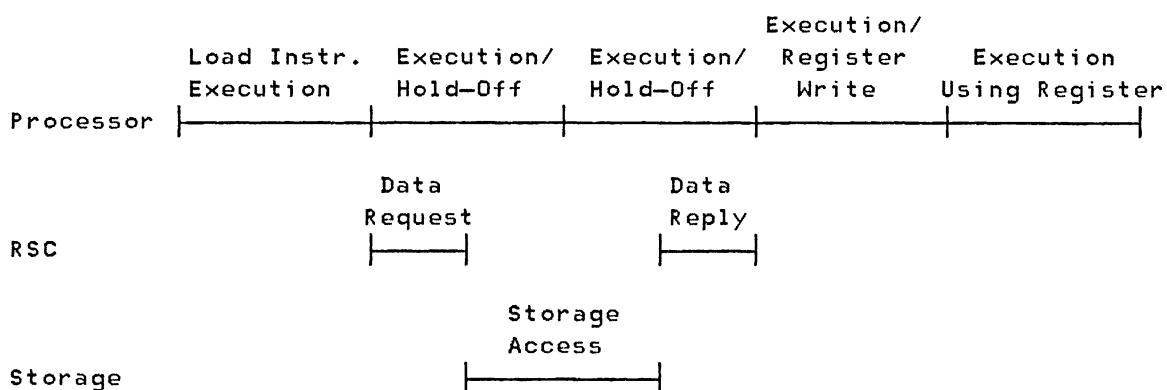

| 11.3 Load Instruction Hold-off . . . . .               | 146 |

| 11.4 I/O Read Hold-Off . . . . .                       | 147 |

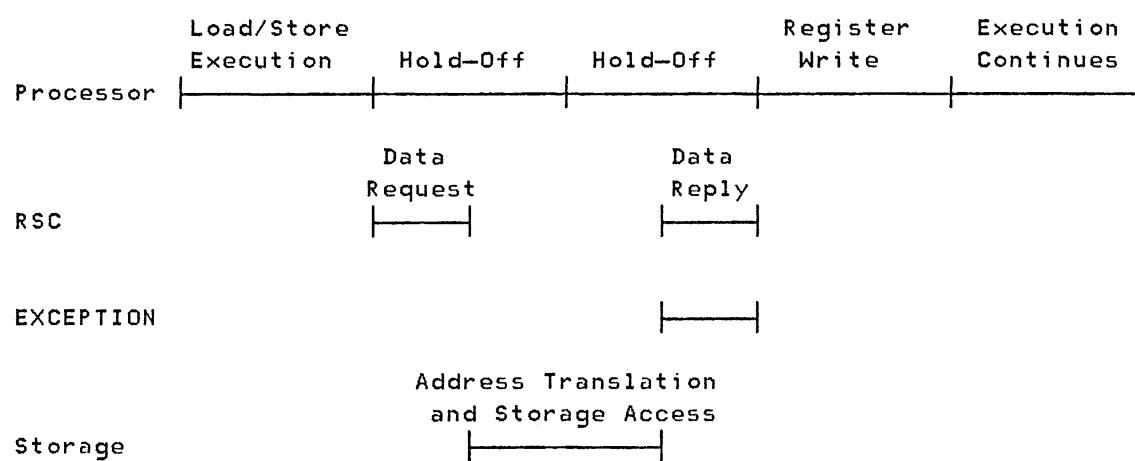

| 11.5 Storage Protect And Address Translation Hold-Off  | 148 |

| 11.6 Tag Hold-Offs . . . . .                           | 149 |

| 11.7 Interrupts . . . . .                              | 149 |

| 11.8 System Timer . . . . .                            | 149 |

| 11.9 Bus Capacity . . . . .                            | 150 |

| 11.10 Selection of Processor Cycle Time . . . . .      | 150 |

| 11.11 Program Performance . . . . .                    | 151 |

| 11.12 Performance Measurement . . . . .                | 153 |

| 12.0 Hardware Description . . . . .                    | 159 |

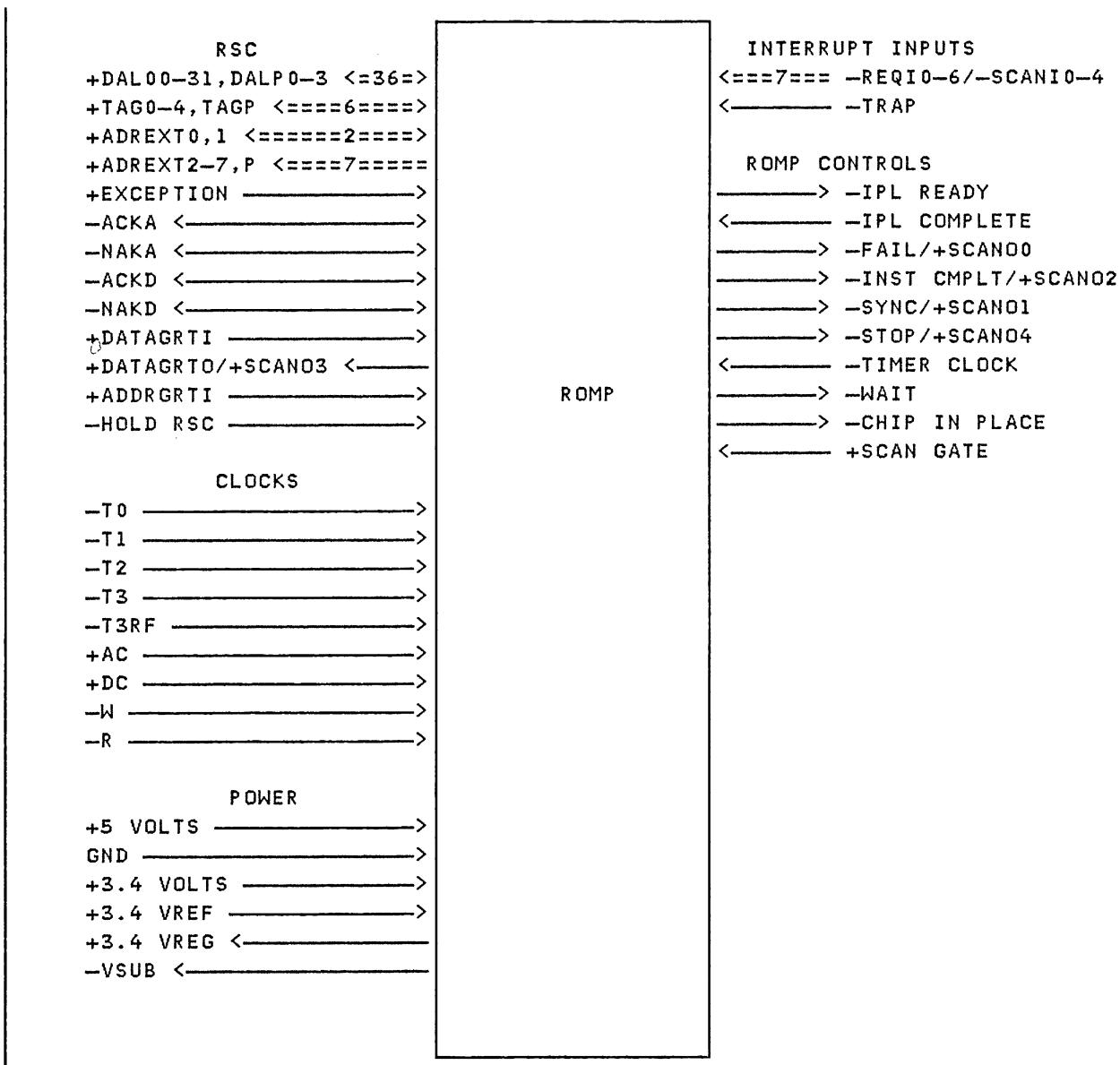

| 12.1 Romp Chip Interfaces . . . . .                    | 159 |

| 12.1.1 ROMP Storage Channel . . . . .                  | 160 |

| 12.1.1.1 RSC Address and Data Bus . . . . .            | 161 |

| 12.1.1.2 RSC Tag Bus . . . . .                         | 162 |

| 12.1.1.3 RSC Address Extension Bus . . . . .           | 162 |

| 12.1.1.4 Exception . . . . .                           | 163 |

| 12.1.1.5 RSC Acknowledge and Not Acknowledge . . . . . | 163 |

| 12.1.1.6 RSC Arbitration . . . . .                     | 163 |

| 12.1.1.7 Hold RSC . . . . .                            | 166 |

| 12.1.2 Clocks . . . . .                                | 166 |

| 12.1.3 Power . . . . .                                 | 166 |

| 12.1.4 Interrupt Inputs . . . . .                      | 167 |

| 12.1.5 ROMP Controls . . . . .                         | 168 |

| 12.1.5.1 IPL Ready . . . . .                           | 168 |

| 12.1.5.2 IPL Complete . . . . .                        | 168 |

| 12.1.5.3 Fail . . . . .                                | 168 |

| 12.1.5.4 Instruction Complete . . . . .                | 169 |

| 12.1.5.5 Sync . . . . .                                | 169 |

| 12.1.5.6 Stop . . . . .                                | 169 |

| 12.1.5.7 Timer Clock . . . . .                         | 169 |

| 12.1.5.8 Wait . . . . .                                | 170 |

| 12.1.5.9 Chip In Place . . . . .                       | 170 |

| 12.1.5.10 Scan Gate . . . . .                          | 170 |

| 12.1.6 Scan Inputs and Scan Outputs . . . . .          | 170 |

| 12.2 ROMP Chip Pin Assignment . . . . .                | 171 |

| 12.3 Processor Signal Description . . . . .            | 172 |

| 13.0 Appendix . . . . .                                | 176 |

| 13.1 Instruction Index By Mnemonic . . . . .           | 176 |

| 13.2 Instruction Index by Op Code . . . . .            | 179 |

| 13.3 Privileged Instructions . . . . .                 | 182 |

| 13.4 Illegal Branch With Execute Subject Instructions  | 183 |

| 13.5 ROMP System Support Software . . . . .            | 184 |

|         |                                                       |     |

|---------|-------------------------------------------------------|-----|

| 13.5.1  | PL.8 Compiler . . . . .                               | 184 |

| 13.5.2  | PASCAL Compiler . . . . .                             | 184 |

| 13.5.3  | C Compiler . . . . .                                  | 185 |

| 13.5.4  | ROMP Development System . . . . .                     | 185 |

| 13.5.5  | PL.8 Source Level Debugger . . . . .                  | 185 |

| 13.5.6  | PL.8 Machine-Level Program Analysis Tool . . . . .    | 185 |

| 13.5.7  | PL.8 Source And Design Code Formatter . . . . .       | 186 |

| 13.5.8  | PL.8 Macro Pre-processor . . . . .                    | 186 |

| 13.5.9  | ROMP Assembler . . . . .                              | 186 |

| 13.5.10 | ROMP Simulator . . . . .                              | 187 |

| 13.5.11 | Program Binder For ROMP . . . . .                     | 187 |

| 13.5.12 | ROMP Hardware Development System . . . . .            | 187 |

| 13.5.13 | Program Development Library (PDL) Interface . . . . . | 187 |

| 13.5.14 | RTIMER Simulator . . . . .                            | 188 |

| 13.6    | ROMP System Hardware References . . . . .             | 188 |

| 13.6.1  | ROMP Engineering Specification . . . . .              | 188 |

| 13.6.2  | ROMP Scan String Definition . . . . .                 | 188 |

| 13.6.3  | Support Processor Interface . . . . .                 | 188 |

| 13.6.4  | ROMP AC Hardware Characterization Plan . . . . .      | 189 |

LIST OF ILLUSTRATIONS

|                                                                                                            |     |

|------------------------------------------------------------------------------------------------------------|-----|

| Figure 1. ROMP System . . . . .                                                                            | 6   |

| Figure 2. Data Units in Main Storage . . . . .                                                             | 6   |

| Figure 3. General Purpose Registers . . . . .                                                              | 10  |

| Figure 4. System Control Registers . . . . .                                                               | 11  |

| Figure 5. Old/New Program Status Pair . . . . .                                                            | 24  |

| Figure 6. Program Status Save Area . . . . .                                                               | 25  |

| Figure 7. Instruction Formats . . . . .                                                                    | 29  |

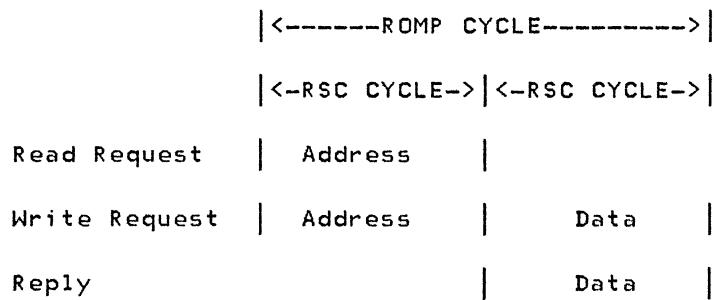

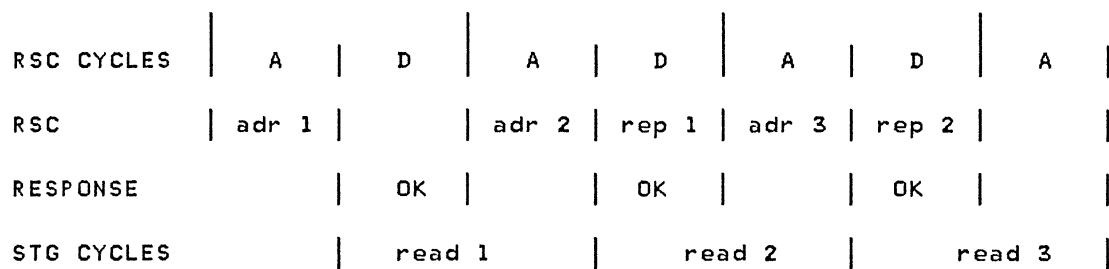

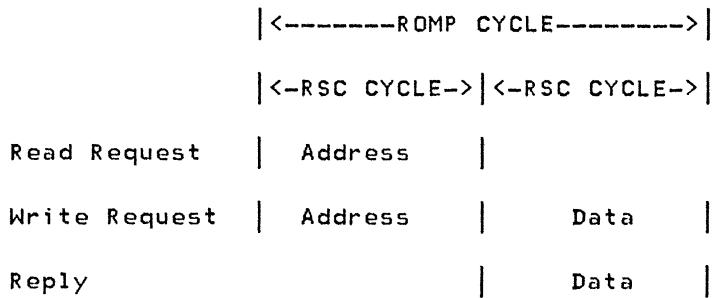

| Figure 8. RSC Transfers . . . . .                                                                          | 93  |

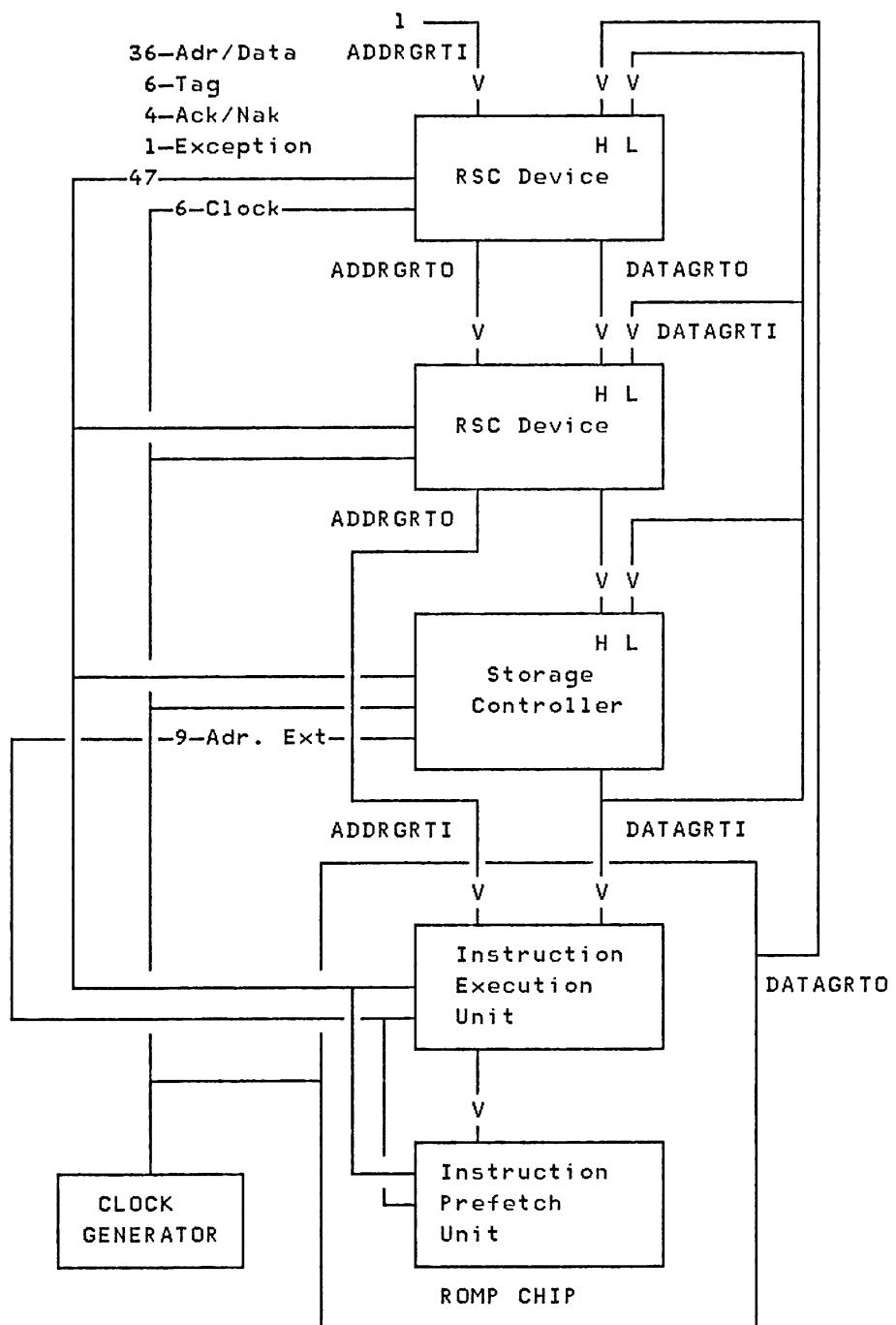

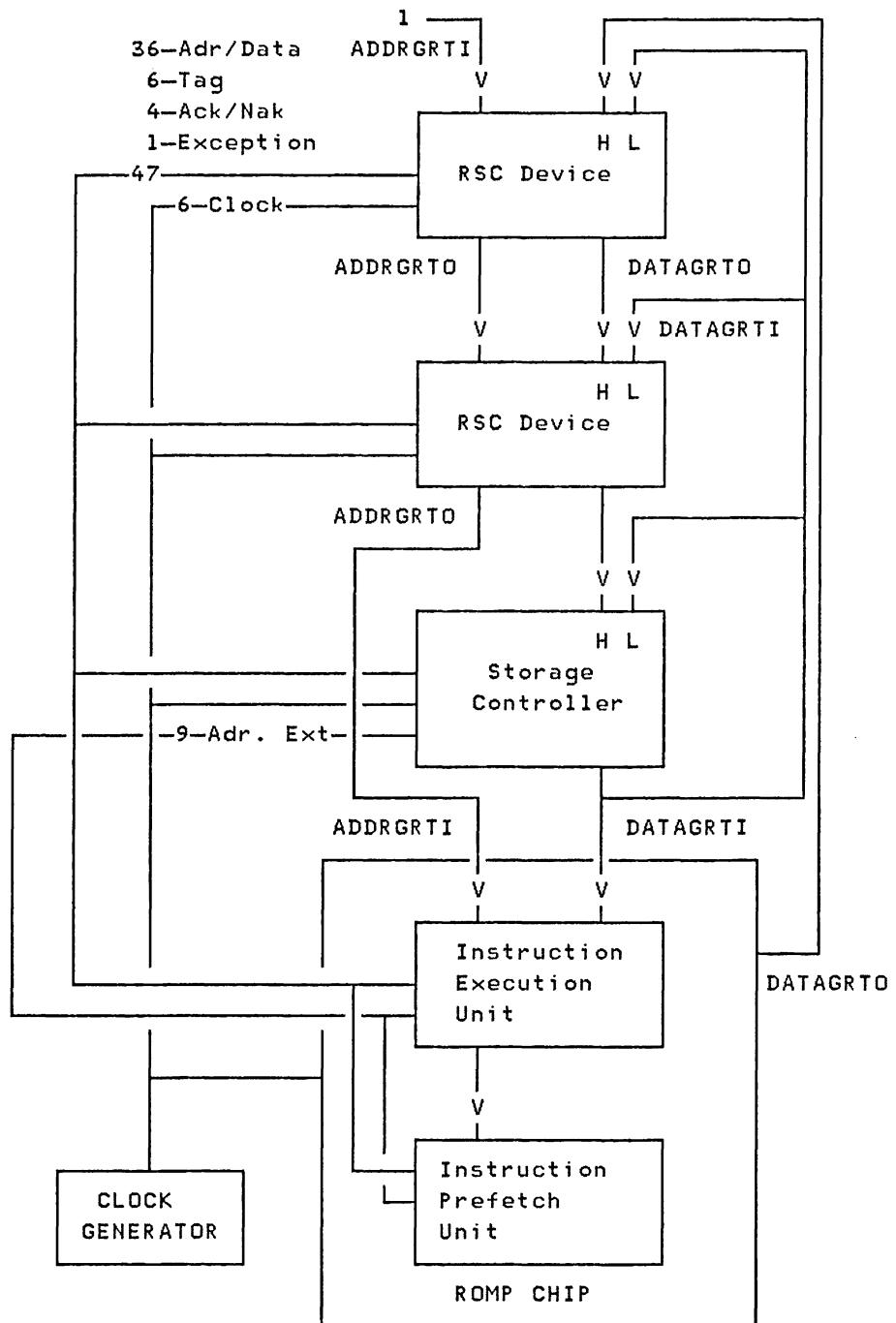

| Figure 9. Typical RSC Configuration . . . . .                                                              | 94  |

| Figure 10. Tag Definition . . . . .                                                                        | 100 |

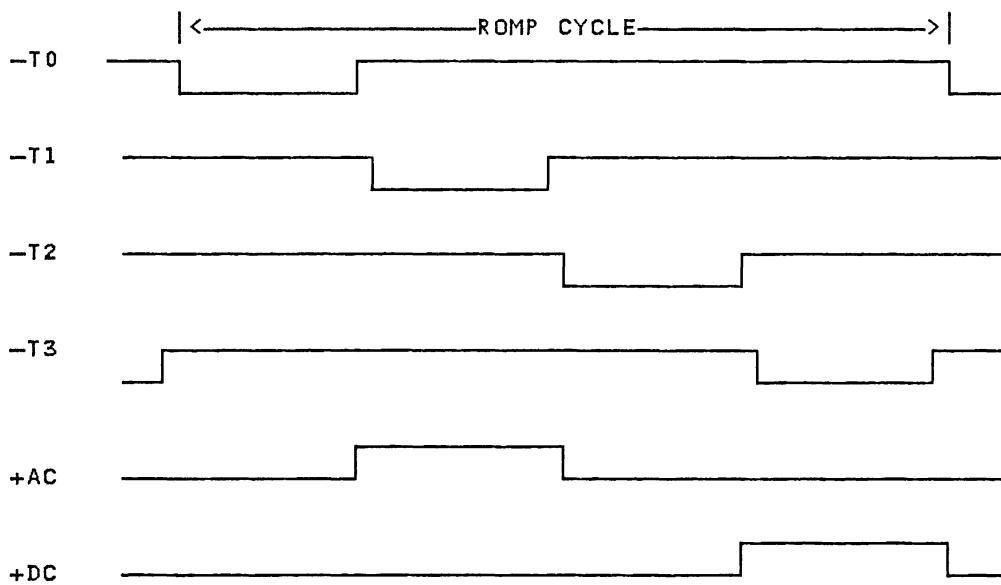

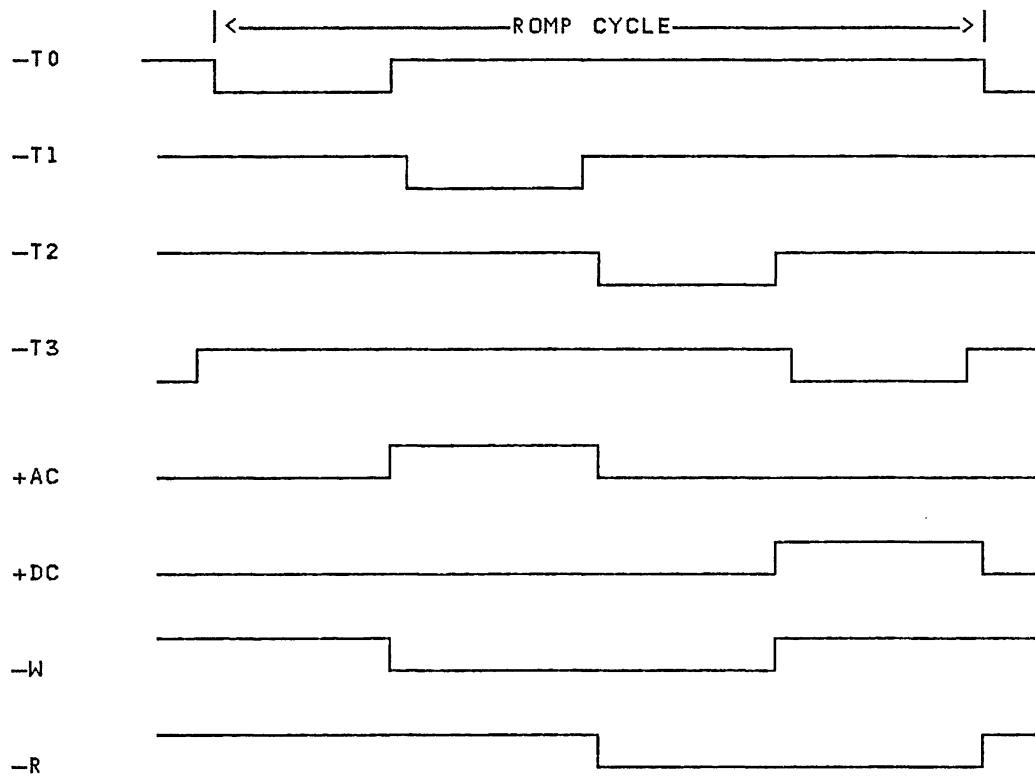

| Figure 11. RSC Clock Timing . . . . .                                                                      | 101 |

| Figure 12. Bus Arbitration Timing . . . . .                                                                | 103 |

| Figure 13. Read Request . . . . .                                                                          | 104 |

| Figure 14. Write Request . . . . .                                                                         | 106 |

| Figure 15. Signal Definitions . . . . .                                                                    | 112 |

| Figure 16. RSC Cycles One Through Three . . . . .                                                          | 113 |

| Figure 17. RSC Cycles Four Through Six . . . . .                                                           | 114 |

| Figure 18. RSC Cycles Seven Through Nine . . . . .                                                         | 115 |

| Figure 19. RSC Cycles Ten Through Twelve . . . . .                                                         | 116 |

| Figure 20. Program Check Errors With Storage Protect And Address Translation Disabled . . . . .            | 127 |

| Figure 21. Program Check Errors With Storage Protect Or Address Translation Enabled . . . . .              | 128 |

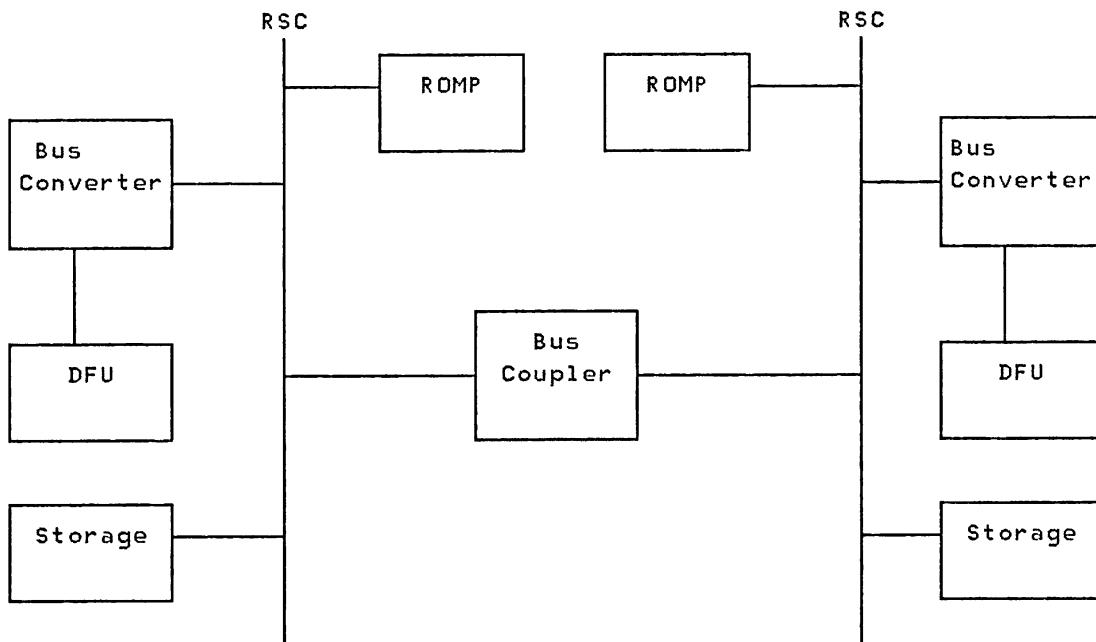

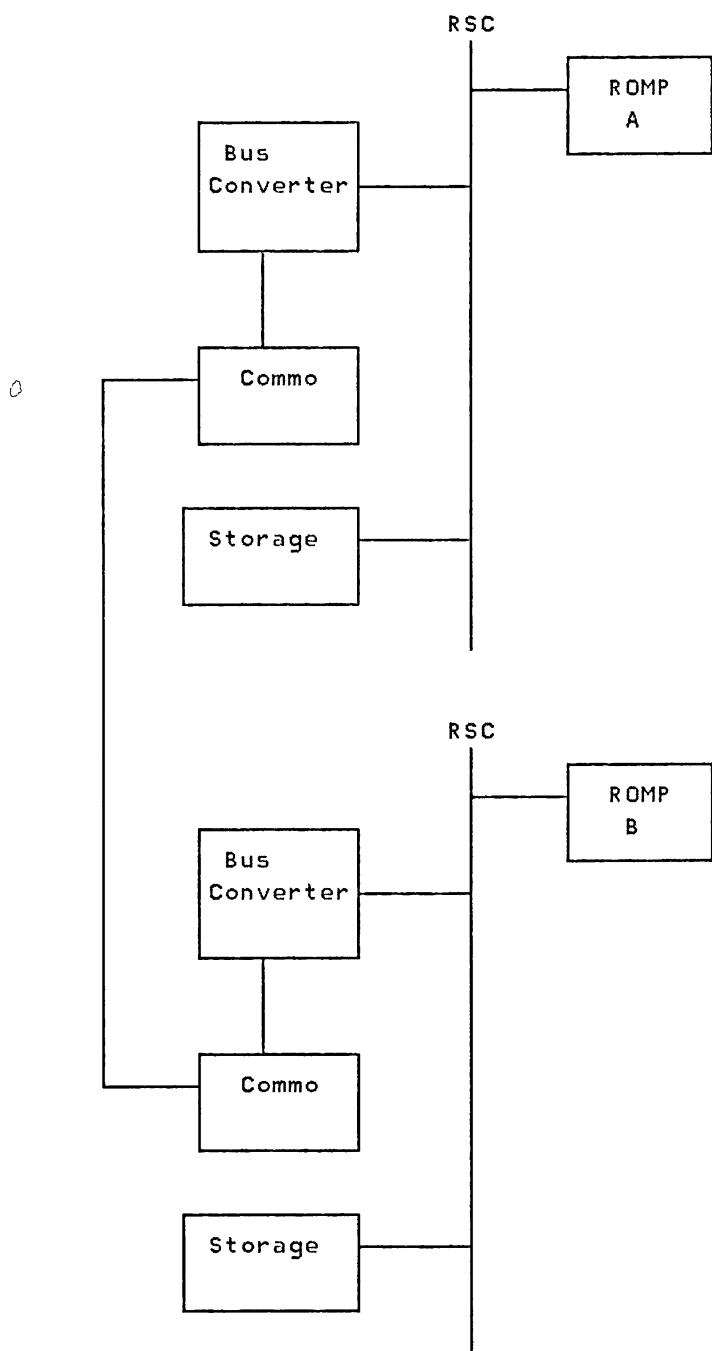

| Figure 22. Multi-Processor Connection Via Common Storage                                                   | 132 |

| Figure 23. Multi-Processor Connection Via Bus Coupler                                                      | 132 |

| Figure 24. Multi-Processor Connection Via Communications Link . . . . .                                    | 133 |

| Figure 25. Storage Controller Timing With Fast Storage                                                     | 134 |

| Figure 26. Storage Controller Timing With Slow Storage                                                     | 135 |

| Figure 27. Storage Controller Timing With ECC . . . . .                                                    | 136 |

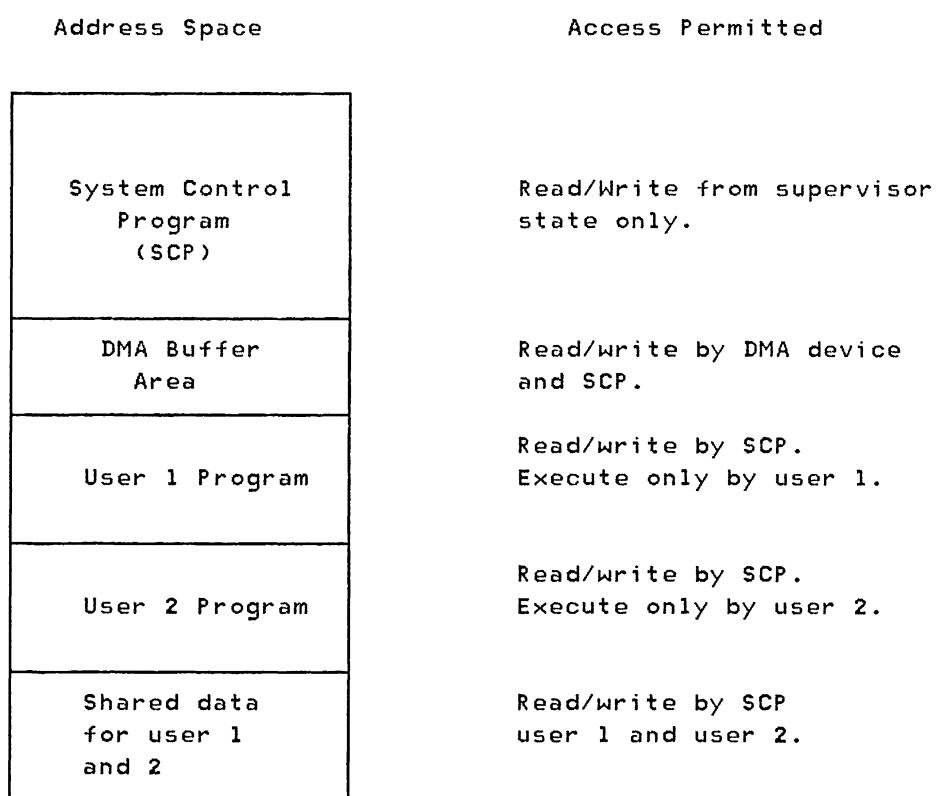

| Figure 28. Typical Storage Protect Assignments . . . . .                                                   | 139 |

| Figure 29. Storage Controller Timing With Address Translation . . . . .                                    | 141 |

| Figure 30. Fetch Timing For New Instruction Stream Following A Successful Branch . . . . .                 | 145 |

| Figure 31. Load Instruction Timing . . . . .                                                               | 147 |

| Figure 32. Load and Store Instruction Timing With Storage Protect or Address Translation Enabled . . . . . | 148 |

| Figure 33. ROMP Module Signals . . . . .                                                                   | 160 |

| Figure 34. RSC Transfers . . . . .                                                                         | 162 |

| Figure 35. Typical RSC Configuration . . . . .                                                             | 165 |

| Figure 36. Clock Timing . . . . .                                                                          | 167 |

| Figure 37. ROMP Module Footprint (Bottom View) . . . . .                                                   | 171 |

## 1.0 INTRODUCTION

### 1.1 DOCUMENT OVERVIEW

This document is the functional specification for the ROMP processor. Information pertaining to the ROMP processor's organization, its instruction set, its I/O capabilities, and its RAS facilities are contained in this document. Other documents are listed in the Appendix which provide additional detailed hardware and software information.

### 1.2 ROMP OBJECTIVES

1. Provide an architected address space of 32-bits. (Choice of 24-bit or 32-bit addressing mode).

2. Provide high performance with fast or slow storage (three MIPS typical with 200 nsec storage).

3. Provide the capability for dynamic address translation.

4. Provide system integrity through the use of storage protect and problem/supervisor states.

5. Provide an efficient target for the PL.8 Compiler.

6. Low power dissipation.

7. Improved debug facilities for IBM products.

### 1.3 ROMP PROCESSOR HIGHLIGHTS

The ROMP processor architecture provides comprehensive facilities for support of many different IBM products. The highlights of the ROMP processor are described here.

The ROMP processor provides 32-bit storage addresses which permits up to 4.3 gigabytes of main storage to be directly accessed. Both instructions and data are contained in main storage.

The address of data in main storage is computed from two values, a base and a displacement, at the time the data is accessed. When data is arranged in blocks, a single base register permits accessing the entire block. Base/displacement addressing allows address field abbreviation in instructions. A base register

permits the instructions which access the data in main storage to be independent of the location of the data.

The processor provides sixteen 32-bit general purpose registers, which are not part of main storage. All arithmetic and logical functions are performed on the general purpose registers which may also function as base registers for base/displacement addressing. The only data operations provided on main storage are loading of data from main storage into a general purpose register and storing of data into main storage from a general purpose register.

The processor also provides sixteen 32-bit system control registers. The system control registers contain the current status of the system. All system control registers may be inspected by the program, and several also can be explicitly modified by the program.

The instruction set includes instructions for accessing storage, arithmetic and logical computations, program and system control including branching, and input/output. An instruction is either two or four bytes in length. The instruction set has been tailored for performance, storage efficiency and function, and has been demonstrated to give high performance in spite of its simplicity.

The ROMP processor supports dynamic address translation in the storage controller. This feature allows a large virtual address space to be mapped into smaller physical address space. ROMP provides an exact interrupt mechanism that allows the processor state to be saved when a storage exception condition occurs. The processor state can then be reloaded after the exception has been handled, and execution of the program continued.

ROMP provides a supervisor state in which all instructions are valid, and a problem state in which only instructions that cannot be used to affect system integrity are valid. ROMP also provides a storage protect mechanism that allows address checking to be implemented in the storage controller. These two features insure that system integrity can be maintained at all times.

The ROMP processor provides a priority interrupt structure. An interrupt at a high priority level preempts ongoing activity at a lower priority level. When an interrupt occurs, only the basic processor status is changed. This primitive status switching permits the flexible programming of dispatching mechanisms.

Two levels of input/output support are provided. For low performance data transfer, programmed I/O (PIO) is synchronous to the issuing program. For high performance data transfer, direct memory access (DMA) permits transferring of data asynchronously to the program.

The ROMP processor implements a high-performance, 32-bit storage channel called the ROMP Storage Channel (RSC). The RSC supports

the high data rate needed for instruction execution, and can also be used for high-speed I/O devices.

The ROMP processor provides facilities for logging errors in the system. The logged information can be used as a basis for isolation of a failing component.

#### 1.4 PROGRAMMING SUPPORT OVERVIEW

The ROMP processor was designed to be an efficient target for the PL.8 high-level language. PL.8 is a derivative of PL/I and has been demonstrated to be well suited to systems programming needs. The compiler for PL.8 uses program flow optimization techniques which produce efficient code in terms of both storage and performance. The high-level language provides improved programmer productivity, quality of code, and migratability of code. It is expected that all but a small percentage of the code for ROMP processors will be written in PL.8.

Other programming aids include an assembly language simulator, a ROMP assembler, and linkage editor which assist the programmer in checking and documenting programs, in controlling address assignment, in segmenting a program, in data and symbol definition, in generating macro instructions, and in controlling the assembler itself.

"ROMP System Support Software" on page 184 contains a summary of support software status and lists available documentation.

#### 1.5 HARDWARE DOCUMENTATION OVERVIEW

The ROMP Functional Specification is designed to provide an architectural description of the ROMP processor, and the ROMP Storage Channel. In addition, it is intended to provide a general description of how the ROMP processor can be employed in various system configurations, and to provide references to additional documentation concerning the detailed electrical and environmental characteristics of the ROMP chip, the ordering of internal registers in the ROMP processor, and a suggested support processor interface definition. The various documents describing these detailed aspects of the ROMP processor are included in "ROMP System Hardware References" on page 188.

#### 1.6 SIGNAL NAMING CONVENTIONS

The terms active and inactive are used throughout this document to describe the state of various signals. All signal names (i.e. +DAL00, +EXCEPTION, -REQIO, etc.) are preceded by a + or -. If the signal name is preceded by a +, an active state is a voltage level of +2.4 volts or greater, and an inactive state is a voltage level of +0.8 volts or less. If the signal name is preceded by a -, an active state is a voltage level of +0.8 volts or less, and an inactive state is a voltage level of +2.4 volts or greater.

## 2.0 SYSTEM ORGANIZATION AND CONTROL

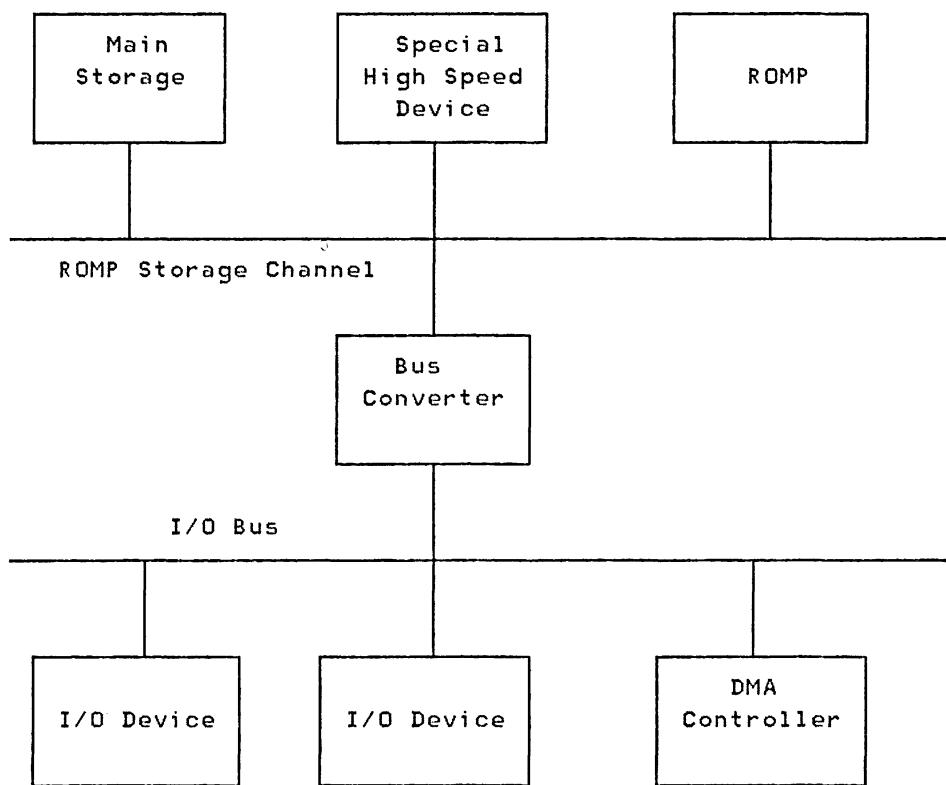

A ROMP system consists functionally of a ROMP, main storage, a bus converter, input/output devices, and possibly a direct memory access (DMA) controller, depending upon I/O device requirements. RSC devices may reference storage without processor involvement.

This structure shown in Figure 1.

### 2.1 MAIN STORAGE

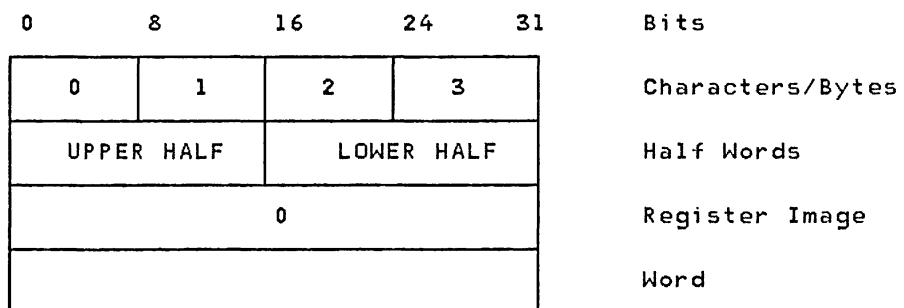

The ROMP system provides directly addressable main storage for data and instructions. The data units in main storage are shown in Figure 2 on page 6.

Up to 4.3 gigabytes of main storage may be directly addressed. Main storage is organized as a sequence of 32-bit words, each consisting of four 8-bit bytes. Bytes in main storage are consecutively numbered, left to right, starting with zero. Each number is considered the address of the corresponding byte. All addresses are computed as byte addresses. The address of a word has zeros in the two low-order bits. The address of a halfword has one zero in the low-order bit. Instructions must be located on halfword boundaries.

All storage effective addresses (base address plus displacement) are computed as 32-bit quantities. Wrap around is allowed and occurs on a 32-bit basis, i.e., main storage addressing wraps around from the architectural maximum byte address of 4,294,967,295 to address 0. This implementation of ROMP supports both 24-bit and 32-bit addressing. Systems which do not require virtual addressing can select the 24-bit addressing mode where the high-order byte of the 32-bit effective address is checked to be zero. A non-zero high-order byte in the effective address will cause a program check condition. Virtual address systems can select the 32-bit addressing mode which disables checking of the upper-byte.

Figure 1. ROMP System

Figure 2. Data Units in Main Storage

## 2.2 STORAGE CHANNEL

ROMP's storage channel provides a 32-bit plus four parity bits wide synchronous bus which cycles at twice the processor cycle rate. The purpose of the channel is to enhance processor performance by having a bus dedicated to processor and storage transfers. All data and addresses transferred on the channel are multiplexed on the 32 address/data lines. An optional address extension bus consisting of 8 address lines plus parity is provided for systems using 32-bit addressing. Devices connected to the storage channel are identified by a five-bit tag identifier that devices put on the storage channel simultaneously with their request. Arbitration is accomplished by using a linear arbitration mechanism with devices connected in a daisy chain. For more information see "ROMP Storage Channel" on page 92.

## 2.3 PROGRAMMED I/O

Programmed I/O is allowed by the use of the Input/Output Read (IOR) and Input/Output Write (IOW) instructions. With these instructions, I/O devices can be read or written synchronously with program execution (see "Input/Output" on page 88).

## 2.4 PROCESSOR

The processor contains the sequencing and processing controls for instruction execution, interrupt action, the system timer and other control related functions.

Instructions are grouped into ten classes: storage access, address computation, branching, traps, moves and inserts, arithmetic, logical operations, shifts, system control, and input/output. A separate sub-section is devoted to each instruction class in "Instruction Set" on page 26.

## 2.5 PROCESSOR STATES

### 2.5.1 Executing Wait Check Stop and Stopped State

Four states of the processor are defined: executing state, wait state, check stop state, and stopped state.

The processor is in the executing state when it is executing instructions. In the executing state, instruction fetching and execution proceeds in the specified manner. Interrupts may occur between instructions as specified in "Interrupts" on page 17.

After the processor has executed the Wait instruction it is in the wait state. No other instructions are fetched or executed while the processor is in the wait state. The processor leaves the wait state and enters the executing state when an interrupt for which the processor is enabled occurs (see "Interrupts" on page 17). The instruction address in the old program status for the priority level associated with the interrupt contains the address of the instruction immediately following the Wait instruction. The I/O pin -WAIT is active when the processor is in the wait state.

When the processor is in the check stop state, no instructions are executed, interrupts do not occur, and system interface operations may be suspended. The processor enters the check stop state when one of the following occurs:

1. An error is detected during power-on diagnostics.

2. A machine check error is detected and the Check Stop Mask is zero.

3. A program check or machine check error is detected and the processor is servicing a machine check error.

4. A program check error is detected and the processor is servicing a program check error.

The check stop condition is cleared during a power-on reset. The processor machine check is described in "Machine-Check Errors" on page 121, and the program check is described in "Program-Check Errors" on page 124.

The stopped state is entered as a result of operator action from a control panel. Operator initiated load, display, and stepping functions occur in the stopped state as described in "Processor Support Functions" on page 142.

#### 2.5.2 Problem and Supervisor States

The selection between problem and supervisor state determines whether the full set of instructions is valid. In supervisor state, all instructions are valid. In problem state, only instructions that cannot be used to affect system integrity are valid. The instructions that are not valid in problem state are called privileged instructions; they include those which inspect or modify any system control registers (except the Condition Status or Multiplier Quotient registers), the Load Program Status

instruction, and the Wait instruction. A privileged instruction encountered in the problem state constitutes a privileged instruction exception and causes a program check. "Privileged Instructions" on page 182 lists the privileged instructions.

The processor is in problem state when bit 21 of the Interrupt Control Status (ICS) is a one. The processor is in supervisor state when bit 21 of the ICS is a zero.

## 2.6 GENERAL-PURPOSE REGISTERS

The processor provides sixteen 32-bit general purpose registers (GPRs). All manipulation of data is performed in the GPRs.

Each GPR consists of an upper and lower half of sixteen bits each. The GPR may be partitioned into four eight-bit characters, C0, C1, C2, and C3. The general purpose register organization is shown in Figure 3 on page 10.

To avoid the destruction of operands in certain operations, some instructions cause the result of the operation to be placed in the twin of one of the GPR operands. The register twin of a given GPR has the name, in binary, of the given GPR with the low-order bit inverted. Thus the twin of GPR 5 (binary 0101) is GPR 4 (binary 0100), and the twin of GPR 14 (binary 1110) is GPR 15 (binary 1111). A register and its twin are referred to as a pair.

For computation purposes, the content of a GPR is treated as either a signed algebraic quantity, an unsigned positive quantity, or an unstructured logical quantity. In a GPR, an algebraic quantity is represented by 32 bits in two's complement form.

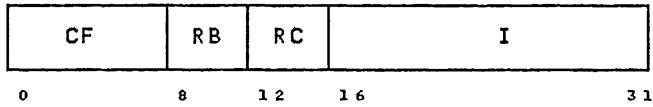

## 2.7 SYSTEM CONTROL REGISTERS

Sixteen 32-bit system control registers (SCR) exist in the processor. An entire SCR or fields within an SCR are assigned to particular facilities in the system such as interrupt, processor, and system timer. The register organization for SCRs is shown in Figure 4. Some SCRs and SCR fields are reserved and are not assigned to any system facility. The source bits are ignored on an attempt to set the reserved bits of an SCR. When the reserved bits of an SCR are fetched, the resulting values are unpredictable.

|  |         |

|--|---------|

|  | 0       |

|  | 1 Pair  |

|  | 2       |

|  | 3 Pair  |

|  | 4       |

|  | 5 Pair  |

|  | 6       |

|  | 7 Pair  |

|  | 8       |

|  | 9 Pair  |

|  | 10      |

|  | 11 Pair |

|  | 12      |

|  | 13 Pair |

|  | 14      |

|  | 15 Pair |

0

31

| Register   |    |            |    | Word           |

|------------|----|------------|----|----------------|

| Upper Half |    | Lower Half |    | Register Half  |

| C0         | C1 | C2         | C3 | Character/Byte |

| 0          | 8  | 16         | 24 | 31             |

Figure 3. General Purpose Registers

|                     |       |        |

|---------------------|-------|--------|

| Reserved            | SCR 0 |        |

| Reserved            | SCR 1 |        |

| Reserved            | SCR 2 |        |

| Reserved            | SCR 3 |        |

| Reserved            | SCR 4 |        |

| Reserved            | SCR 5 |        |

| Counter Source      | SCR 6 |        |

| Counter             | SCR 7 |        |

| Reserved            | TS    | SCR 8  |

| Reserved            | SCR 9 |        |

| Multiplier Quotient |       | SCR 10 |

| Reserved            | MCS   | PCS    |

| Reserved            | IRB   |        |

| IAR                 |       | SCR 13 |

| Reserved            | ICS   |        |

| Reserved            | CS    |        |

0 8 16 24 31

COUS = Counter Source

COU = Counter

TS = Timer Status

MQ = Multiplier Quotient

MCS = Machine Check Status

PCS = Program Check Status

IRB = Interrupt Request Buffer

IAR = Instruction Address Register

ICS = Interrupt Control Status

CS = Condition Status

Figure 4. System Control Registers

#### 2.7.1 Counter Source Counter and Timer Status

The Counter Source (COUS, SCR 6), Counter (COU, SCR 7), and Timer Status (TS, SCR 8) are necessary for the system timer operation and are described in "System Timer Facility" on page 14.

#### 2.7.2 Multiplier Quotient

SCR 10 is referred to as the Multiplier Quotient (MQ). The MQ provides a GPR extension to accommodate the product for the Multiply Step instruction and the dividend for the Divide Step instruction (see "Divide And Multiply Step Instructions" on page 65).

#### 2.7.3 Machine Check Status and Program Check Status

Bits 16-23 of SCR 11 are referred to as the Machine Check Status (MCS) and bits 24-31 are referred to as the Program Check Status (PCS). These two fields are used for error identification and are described in detail in "Machine-Check Errors" on page 121 and "Program-Check Errors" on page 124.

#### 2.7.4 Interrupt Request Buffer

Bits 16-31 of SCR 12 are referred to as the Interrupt Request Buffer (IRB). The Interrupt Request Buffer allows interrupt requests to be generated under program control. For more detailed information refer to "Interrupt Request Buffer" on page 21.

#### 2.7.5 Instruction Address Register

SCR 13 is referred to as the Instruction Address Register (IAR). The Instruction Address Register is a 32-bit register which contains the address of the next instruction to be executed. Since all instructions lie on halfword boundaries, the low-order bit (bit 31) of the Instruction Address Register is zero. Accesses for instructions may require the fetching of a word, a halfword, or the low-order halfword of a word followed by the high-order halfword of the next consecutive word in main storage.

Logically, during the execution of an instruction, the content of the Instruction Address Register is incremented by the length of the current instruction. Should this instruction be a successful branch/jump instruction, the content of the Instruction Address Register is changed to the address of the branch/jump target instruction. The IAR contains the address of the next instruction when the IAR is saved as part of the program status and when a system control instruction to read the IAR is executed.

#### 2.7.6 Interrupt Control Status

Bits 16-31 of SCR 14 are referred to as the Interrupt Control Status (ICS). The ICS contains the Parity Error Retry Interrupt Enable bit, Storage Protect bit, Problem State bit, Translate Mode bit, Interrupt Mask, Check Stop Mask, Register Set Number, and the Processor Priority. The ICS is described in "Interrupt Control Status" on page 21.

#### 2.7.7 Condition Status

Bits 16-31 of SCR 15 are referred to as the Condition Status (CS). The Condition Status contains information about the results of certain operations and provides a mechanism for decision making. The Condition Status is defined as follows:

|            |                     |

|------------|---------------------|

| Bits 16-23 | Reserved            |

| Bit 24     | Permanent Zero (PZ) |

| Bit 25     | Less Than (LT)      |

| Bit 26     | Equal (EQ)          |

| Bit 27     | Greater Than (GT)   |

| Bit 28     | Carry Zero (C0)     |

| Bit 29     | Reserved            |

| Bit 30     | Overflow (OV)       |

| Bit 31     | Test Bit (TB)       |

Bit 24 of the Condition Status is the Permanent Zero bit (PZ). It is set to zero whenever the Condition Status is loaded, and it cannot be set to one. Its presence provides for a guaranteed branch or jump by use of a branch on not condition bit or jump on not condition bit instruction specifying the Permanent Zero bit.

Bit 25 of the Condition Status is the Less Than bit (LT). This bit is set to one during logical, shift, and certain arithmetic instructions if the result is negative or if the high-order bit of the result is one; otherwise it is set to zero. It is also set during compare instructions to indicate the relative algebraic magnitudes of the comparands.

Bit 26 of the Condition Status is the Equal bit (EQ). This bit is set to one during logical, shift, and certain arithmetic instructions if all bits of the result are zeros; otherwise it is set to zero. It is also set during compare instructions if the comparands are equal.

Bit 27 of the Condition Status is the Greater Than bit (GT). This bit is set to one during logical, shift, and certain arithmetic instructions if the sign bit of the result is zero and the result is nonzero; otherwise it is set to zero. It is also set during compare instructions to indicate the true relative algebraic magnitudes of the comparands.

Bit 28 of the Condition Status is the Carry Zero bit (C0). This bit is set to one during certain arithmetic instructions if the operation generates a carry out of bit position zero; otherwise it is set to zero.

Bit 29 of the Condition Status is a reserved bit.

Bit 30 of the Condition Status is the Overflow bit (OV). It is set to one during certain arithmetic instructions if the signed result of the operation cannot be represented in 32 bits; otherwise it is set to zero.

Bit 31 of the Condition Status is the Test bit (TB). It is set by the move to test bit instructions, where a specified bit of the half of a register is moved to the test bit. It is also affected by instructions which load or directly alter the Condition Status register.

All bits of the Condition Status, except the Permanent Zero bit, can be set through use of the move to SCR instructions.

A four-bit field in the conditional branch instructions specifies the Condition Status bit to be tested. A zero in the four-bit field of a branch instruction specifies bit 16 of the Condition Status, a one specifies bit 17 of the Condition Status, and so on. A three-bit field in the conditional jump instructions specifies the Condition Status bit to be tested. A zero in this three-bit field specifies bit 24, a one specifies bit 25, and so on.

## 2.8 SYSTEM TIMER FACILITY

Many applications require a knowledge of real time for such functions as system counting, time slicing, time stamping, interval timing, and timing the productivity of operations. These functions can be provided using the system timer facility.

For some devices, the device requirements may be such that additional timers are needed in the adapter. A more sophisticated timer can be provided as an I/O device if needed.

System timer updating occurs at the frequency of the clock connected to the timer clock I/O pin.

This section describes the system timer facility and its operation.

0

#### 2.8.1 Counter

SCR 7 is referred to as the Counter (COU) and is a thirty-two-bit count-down counter. The Counter is decremented from an external source connected to the I/O pin -TIMER CLOCK. The counter is updated on an inactive to active transition of -TIMER CLOCK. Processor instruction execution is suspended during the counter update. When the Counter is decremented from 1 to 0, the value contained in the Counter Source is loaded into the Counter and the alarm action is initiated. This action is such that normal operations will continue by the time the next count pulse arrives. The alarm action is to set a bit in the IRB whose priority level corresponds to the Timer Interrupt Priority in SCR 8, if the timer is enabled. The alarm also sets the Interrupt Status bit to one, and updates the Timer Status. The contents of the Counter Source are not altered.

#### 2.8.2 Counter Source

The Counter Source (COUS), SCR 6, consists of the thirty-two-bit value that is automatically loaded into the Counter when an alarm occurs.

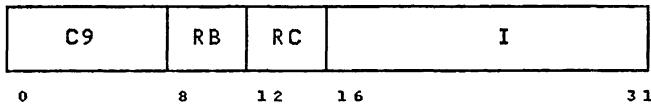

#### 2.8.3 Timer Status

The Timer Status (TS), bits 24-31 of SCR 8, is defined as follows:

Bit 24      Reserved.

Bit 25      Enable. When zero, no interrupts are created. This does not start or stop the counter, but enables/disables the setting of IRB bits. At power-on reset, this bit is zero.

|            |                                                                                                                                                                                                                                                                               |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 26     | Interrupt Status. When one, an alarm has occurred. This bit is set only if an alarm has occurred, and the Enable bit is set to one. This bit is reset by software when the counter is serviced. Software can reset this bit by executing a Clear SCR Bit (CLRSB) instruction. |

| Bit 27     | Overflow. When one, more than one alarm has occurred before the Interrupt Status bit has been reset. This bit is also reset by software when the counter is serviced.                                                                                                         |

| Bit 28     | Reserved                                                                                                                                                                                                                                                                      |

| Bits 29-31 | Timer Interrupt Priority. A timer alarm causes the setting of an IRB bit corresponding to the priority level specified by this field if the timer is enabled.                                                                                                                 |

#### 2.8.4 Programming Note: System Timer Operation

To provide an interval timer, the Counter is directly loaded with a value corresponding to the amount of time until the interval is to expire.

To provide a fixed interval interrupt, an appropriate value is loaded into the Counter Source and then not changed. For example, if the Counter Source was loaded with 5 (X'05'), and a 1 millisecond timer clock was used, the processor would be interrupted every 5 milliseconds; if it was loaded with 250 (X'FA'), the processor would be interrupted every one-fourth second. Software could then update internal storage locations and provide time-of-day in whatever format desired.

Note that loading the Counter Source does not alter the value in the Counter. As a result, the interrupt interval corresponding to the value loaded into the Counter Source will not begin until the Counter is decremented from 1 to 0, and the new Counter Source is loaded into the counter. To synchronize the Counter with a new Counter Source, both the Counter Source and the Counter must be loaded with the new Counter Source value.

Multiple simultaneous timings can be handled using the system timer as a resource. The Counter is loaded from a queue whose entries are calculated to be the "time" from the completion of the previous entry until the time for the entry in question to be completed.

The external clock allows the system timer to be used to count external events and can notify the program when a specific count

arrives. This source need not provide a regular, clock-like signal; it can be either a regular or irregular source.

The value loaded into the Timer Interrupt Priority (TS, bits 29-31) must be greater than or equal to zero (000) and less than or equal to six (110). These are the only values for which a corresponding IRB exists. A value of seven (111) in the Timer Interrupt Priority will cause no bit in the IRB to be set when a timer interrupt occurs.

## 2.9 INTERRUPTS

The Interrupt facility permits the processor to change its status at the request of some other system component or due to processor conditions established by the program. Interrupt processing consists of saving the current program status and establishing the program status for servicing the interrupt. Interrupts only occur on instruction boundaries, but some instruction sequences are not interruptible. A Load Program Status (LPS) instruction is provided for software to return from an interrupt. Execution of a LPS instruction restores the IAR, the CS, and the ICS to the values that existed when the interrupt occurred (see "Load Program Status Instruction" on page 85).

The processor may also change its status as a result of error conditions within the processor or a system component. Error processing consists of saving the current program status and establishing the program status for servicing the error. Errors are grouped into two classes: Machine check errors and program check errors. These errors are discussed in detail in "Reliability, Availability, and Serviceability" on page 121.

The interrupt facility is a priority-based mechanism. This permits the servicing of higher priority functions to take precedence over the servicing of lower functions.

Interrupt sources consist of the seven external interrupt inputs (-REQI0-6), software interrupts posted via setting of bits in the IRB, and error conditions (either the -TRAP input, or internal errors) detected during system operation. The seven external interrupt inputs and software setting of IRB interrupt request bits are treated in the same manner by ROMP. The interrupt request level is compared to the current processor priority specified by bits in the ICS. If the interrupt request represents a higher priority than the current processor priority, and interrupts are enabled by the Interrupt Mask in the ICS, then the interrupt is taken.

Taking an interrupt consists of saving the current processor status in the old PSW corresponding to the level of the interrupt request, and loading a new processor status from the new PSW

corresponding to the level of the interrupt request. Saving of the current processor status requires saving the address of the instruction, the condition status, and the ICS when the interrupt occurred. Loading of the new processor status requires loading the new IAR (containing the address of the interrupt service routine) and the new ICS from the new PSW. Saving of the current processor status and loading of the new processor status is performed automatically by ROMP hardware. Note that none of the GPRs are automatically saved by hardware. Software is responsible for saving any GPRs modified by the interrupt service routine. Once the interrupt has been serviced, execution of the old program can be resumed by loading the old program status word via an LPS instruction. This will restore the IAR, the CS, and the ICS to the values that existed when the interrupt occurred.

In addition to the seven interrupt levels, the detection of error conditions can cause interrupts to the Program Check and Machine Check interrupt levels. Interrupts to the Program Check level consists of errors which are most probably due to software errors (i.e. detection of an invalid op-code, addressing error, detection of a privileged instruction exception, etc.). Interrupts to the Machine Check level consists of errors which are most probably due to hardware errors (i.e. RSC parity errors, and RSC timeouts). In addition, an external input (-TRAP) can be used by system components to cause a machine check interrupt. "Machine-Check Errors" on page 121 and "Program-Check Errors" on page 124. describe Machine Check and Program Check interrupts.

#### 2.9.1 Processor Priority

Under normal system conditions, the processor executes instructions at a level of priority referred to as the Processor Priority. The Processor Priority may assume one of eight levels as specified by a three-bit field in the ICS. Priorities for the eight levels are represented by the following inequality:

Priority of Level 0 > Priority of Level 1 >...> Priority of Level 7

The Processor Priority may be changed either by an interrupt or by an instruction which modifies the Processor Priority. There are two sources of interrupts: an interrupt condition signaled via the Interrupt Request Buffer, or an interrupt condition signaled by some system component via the seven interrupt request inputs (-REQI0-6).

The processor may also execute instructions at two levels which are not accessible via the interrupt facility. These levels are provided for the reporting and servicing of machine check and program check error conditions as discussed in "Machine-Check

Error Handling" on page 122 and "Program-Check Error Handling" on page 124.

#### **2.9.1.1 Interrupt Request Priority**

Interrupt requests occur on one of seven priority levels. Priorities for the seven levels are represented by the following inequality:

Priority of level 0 > Priority of Level 1 >...> Priority of Level 6

The processor may execute instructions with a processor priority of 7, but no interrupt requests with a priority of seven can occur.

#### **2.9.1.2 Interrupt Priority Assignment**

A bit being set to one in the Interrupt Request Buffer causes an interrupt request to the level corresponding to that bit. Timer interrupts cause an interrupt request (via the IRB) to the level specified in the Timer Status. A system component causes an interrupt request at a level determined by the attachment of its Interrupt Request line (-REQI0 through 6) to the processor.

#### **2.9.2 Point of Interrupt**

Interrupts only occur on instruction boundaries. Furthermore, interrupts are prevented from occurring within certain instruction sequences. A branch with execute instruction and its subject instruction are uninterruptable.

Thus, a branch with execute and its subject instruction is considered to be a unit, and interrupts only occur before or after the unit is executed (refer to "Instruction Set" on page 26).

#### **2.9.3 Error Handling**

If the processor is executing an error routine as a result of a machine check or program check error condition, all interrupt requests from system components and interrupts signaled via the IRB remain pending.

#### 2.9.4 Program Status

The state of the processor is called the program status. The program status consists of the contents of the following system control registers: the Instruction Address Register, the Condition Status, and the Interrupt Control Status.

Upon interrupt the current program status is automatically saved in the old program status location. The program status for servicing the interrupt is loaded from the new program status location, with the exception of the Condition Status. The Condition Status is not changed by loading the new program status.

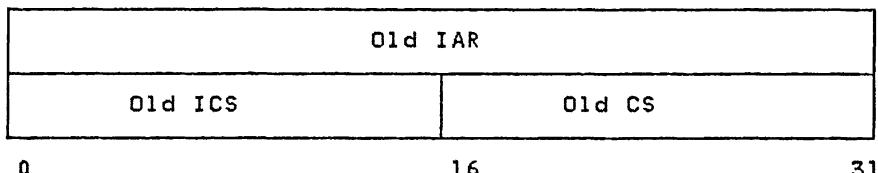

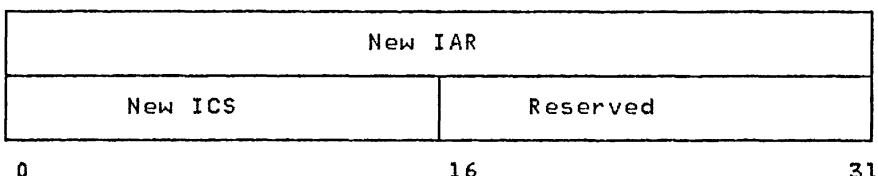

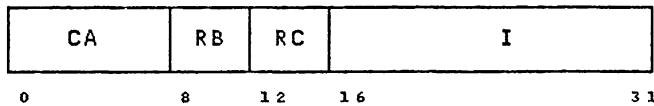

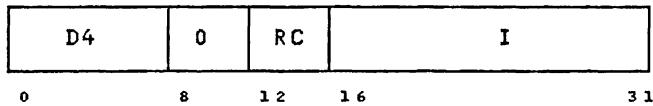

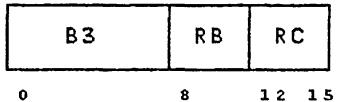

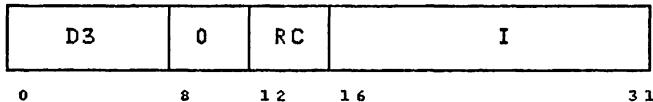

##### 2.9.4.1 Old/New Program Status Pairs

An old/new program status pair consists of eight bytes of old program status and eight bytes of new program status. When an interrupt occurs, the old/new program status pair is specified by the priority level of the interrupt.

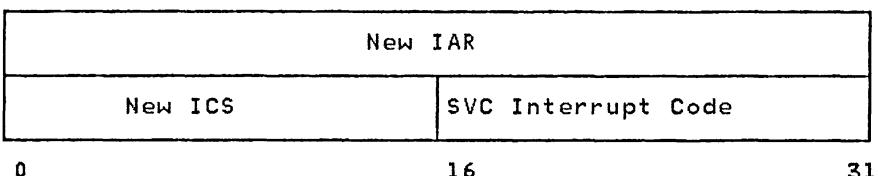

##### 2.9.4.2 Location of Old/New Program Status Pairs

The program status save area in main storage contains ten old/new program status pairs. Two old/new program status pairs are for machine check and program check error handling, one old/new program status pair is used for the Supervisor Call (SVC) instruction, and the remaining seven are for interrupt servicing. The structure of an old/new program status pair is shown in Figure 5 on page 24. Note that the SVC old/new program status pair contains a sixteen-bit SVC interrupt code which is generated by execution of the SVC instruction (See "Supervisor Call Instruction" on page 87). Figure 6 on page 25 shows the organization of the program status save area in main storage. The 16-byte old/new program status pairs are located in consecutive main storage locations. The program status save area is located at addresses X'100' thru X'19F'. Address translation is disabled for storing of the old program status and loading of the new program status.

#### 2.9.5 System Control Registers

Two fields are provided within the system control registers to support the interrupt facility. They are the Interrupt Request Buffer and the Interrupt Control Status.

### 2.9.5.1 Interrupt Request Buffer

The Interrupt Request Buffer (IRB) is a 16-bit field in SCR 12 and has the following format:

|            |                           |

|------------|---------------------------|

| Bit 16     | Interrupt Request Level 0 |

| Bit 17     | Interrupt Request Level 1 |

| Bit 18     | Interrupt Request Level 2 |

| Bit 19     | Interrupt Request Level 3 |

| Bit 20     | Interrupt Request Level 4 |

| Bit 21     | Interrupt Request Level 5 |

| Bit 22     | Interrupt Request Level 6 |

| Bits 23-31 | Reserved                  |

The IRB provides the capability of generating interrupt requests under software control. Setting an IRB bit to one causes an interrupt request to the level corresponding to that bit. The interrupt request remains active until the bit is cleared by software.

If bit 25 of SCR 8 is one (enabled), a timer alarm caused by the Counter being decremented from 1 to 0 sets a bit in the IRB, which generates an interrupt request. The bit in the IRB which is set is determined by the Timer Interrupt Priority in the Timer Status.

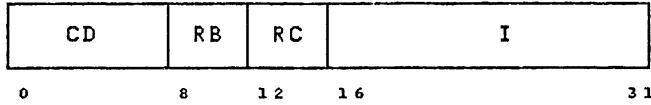

### 2.9.5.2 Interrupt Control Status

The Interrupt Control Status (ICS) is a 16-bit field in SCR 14 with the following format:

|            |                                     |

|------------|-------------------------------------|

| Bits 16-18 | Reserved                            |

| Bit 19     | Parity Error Retry Interrupt Enable |

| Bit 20     | Storage Protect                     |

| Bit 21     | Problem State                       |

| Bit 22     | Translate Mode                      |

| Bit 23     | Interrupt Mask                      |

| Bit 24     | Check Stop Mask                     |

| Bits 25-27 | Register Set Number                 |

| Bit 28     | Reserved                            |

| Bits 29-31 | Processor Priority                  |

A value of one in the Parity Error Retry Interrupt Enable bit enables interrupts when a ROMP Storage Channel (RSC) retry successfully completes a processor generated transfer that was previously unsuccessful due to detection of a parity error. A successful parity error retry interrupt will cause a level 0 interrupt by setting the Interrupt Request Level 0 bit (bit 16) in the Interrupt Request Buffer. The RSC Check bit (bit 16) in the Machine Check Status will be set to indicate the cause of the interrupt.

A value of one in the Storage Protect bit enables address checking in the storage controller. Use of Storage Protect is described in "Storage Protect" on page 137.

A value of one in the Problem State bit places the processor in problem state; a value of zero places the processor in supervisor state.

A value of one in the Translate Mode bit enables address translation in the storage controller. Use of Translate Mode is described in "Address Translation" on page 140.

A value of one in the Interrupt Mask inhibits all system component, timer, and software interrupts on all levels. An interrupt which is inhibited remains pending.

A value of one in the Check Stop Mask prevents the processor from entering the Check Stop state upon the detection of a machine check error.

The three-bit encoded Register Set Number allows one of eight register sets to be specified as the active register set. The current ROMP design implements one of the eight register sets. Bits 25-27 are ignored in this implementation.

The three-bit encoded Processor Priority indicates the current processor priority level. Interrupt requests with priorities lower than or equal to the current processor priority are ignored.

#### 2.9.6 Occurrence of Interrupts

An interrupt occurs due to a bit in the IRB being equal to one if the Processor Priority is lower than the priority corresponding to that bit of the IRB, the Interrupt Mask is zero, and no system component is signaling an interrupt request on a higher level than that signaled via the IRB.

An interrupt occurs due to a system component interrupt request if the Processor Priority is lower than that of the interrupt request, the Interrupt Mask is zero, and the IRB is not signaling an interrupt request on a higher level than that signaled by the system component.

#### 2.9.7 Programming Note: Interrupt Facility

The interrupt facility contains features which, if used improperly, may force the processor into an infinite hardware

loop. When the processor loads the new program status for servicing an interrupt, it loads the Processor Priority from the ICS in the new program status location. The value in the Processor Priority in the new program status is completely under software control. This processor priority which is loaded must not be lower than the priority of the interrupt request which caused the interrupt, if the Interrupt Mask in the new program status is zero, the same interrupt request will immediately cause another interrupt. Multiple interrupts would continue to occur until a system component signals an interrupt request on a higher level, or a power-on reset occurs.

#### 2.9.8 Programming Notes: Interrupt Servicing

The program should issue an IOW instruction to signal the device that the interrupt request is being serviced, and to reset the interrupt request bit in the device status.

1. The program should clear the interrupt request of the interrupting device as soon as possible after the point of interrupt. This allows the processor to determine the priority of the next highest interrupt request.

2. A Load Program Status (LPS) instruction is provided for software to return from an interrupt (see "Load Program Status Instruction" on page 85). The effective address of the LPS instruction points to the Program status to which control is being returned. Normally control will be returned to the previously active program whose program status is located in the old program status associated with the interrupt being serviced.

### Old Program Status

### New Program Status

SVC New Program Status

IAR = Instruction Address Register

ICS = Interrupt Control Status

CS = Condition Status

SVC = Supervisor Call

Note: Reserved bits in the old program status are set to unpredictable values. Reserved bits in the new program status are ignored.

Figure 5. Old/New Program Status Pair

|                |                               |

|----------------|-------------------------------|

| Address X'100' | OLD/NEW PS PAIR 0             |

| Address X'110' | OLD/NEW PS PAIR 1             |

| Address X'120' | OLD/NEW PS PAIR 2             |

| Address X'130' | OLD/NEW PS PAIR 3             |

| Address X'140' | OLD/NEW PS PAIR 4             |

| Address X'150' | OLD/NEW PS PAIR 5             |

| Address X'160' | OLD/NEW PS PAIR 6             |

| Address X'170' | MACHINE CHECK OLD/NEW PS PAIR |

| Address X'180' | PROGRAM CHECK OLD/NEW PS PAIR |

| Address X'190' | SVC OLD/NEW PS PAIR           |

Main Storage Addresses X'100' Through X'19F'

Note: Each PS pair requires 16 bytes.

Figure 6. Program Status Save Area

### 3.0 INSTRUCTION SET

#### 3.1 GENERAL DESCRIPTION

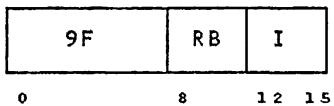

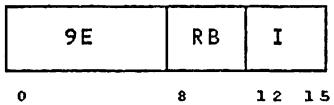

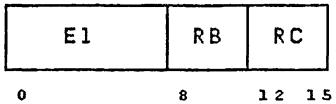

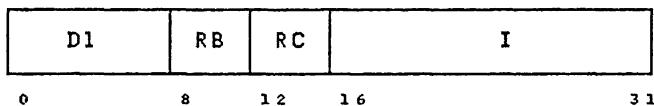

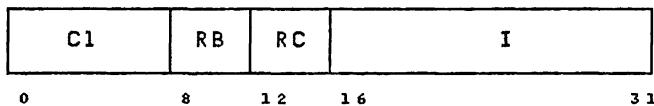

Instructions are grouped into ten classes: storage access, address computation, branching, traps, moves and inserts, arithmetic, logical operations, shifts, system control, and input/output. A separate section is devoted to each instruction class. Each instruction is specified in terms of mnemonic, operation code (op code), length, and functional description.

Unassigned op codes are reserved for future use. If these reserved op codes are encountered by the processor, a program check error occurs. For more detailed information, see "Program-Check Errors" on page 124.

The ROMP processor does not support dynamic instruction modification. Any attempt by software to modify an instruction may result in unpredictable operation.

ROMP provides a supervisor state in which all instructions are valid, and problem state in which only instructions that cannot be used to affect system integrity are valid. The instructions that are not valid in problem state are called privileged instructions. A privileged instruction encountered in the problem state constitutes a privileged instruction exception and causes a program check.

The following notation is used to describe each instruction:

|     |                                                                           |

|-----|---------------------------------------------------------------------------|

| GPR | General Purpose Register (The word register is also used to denote a GPR) |

| SCR | System Control Register                                                   |

| IAR | Instruction Address Register                                              |

| IRB | Interrupt Request Buffer                                                  |

| MCS | Machine Check Status                                                      |

| PCS | Program Check Status                                                      |

| CS  | Condition Status                                                          |

| ICS | Interrupt Control Status                                                  |

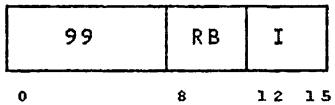

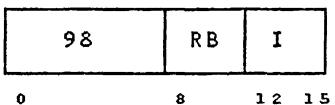

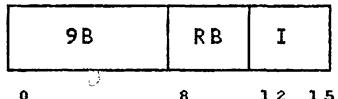

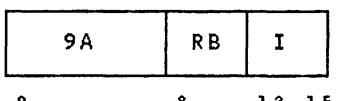

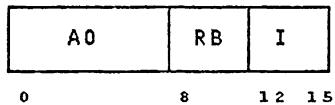

|              |                                                                                                                                                                                                                                                                                                                         |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RA, RB or RC | These abbreviations denote fields in the instruction which specify GPRs.                                                                                                                                                                                                                                                |

| SRB          | This denotes a field in the instruction which specifies an SCR.                                                                                                                                                                                                                                                         |

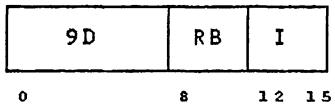

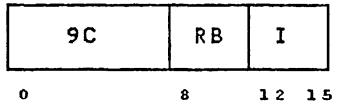

| I            | This denotes a field of immediate data in the instruction.                                                                                                                                                                                                                                                              |

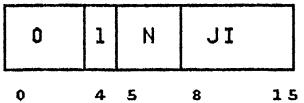

| N            | This denotes a Condition Status bit number.                                                                                                                                                                                                                                                                             |

| JI           | This denotes an eight-bit relative branch displacement in the JI format instructions.                                                                                                                                                                                                                                   |

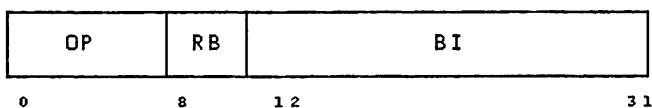

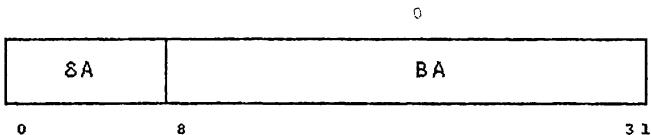

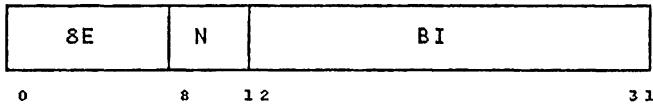

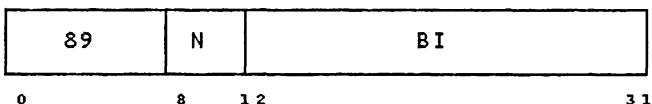

| BI           | This denotes a 20-bit relative branch displacement in the BI format instructions.                                                                                                                                                                                                                                       |

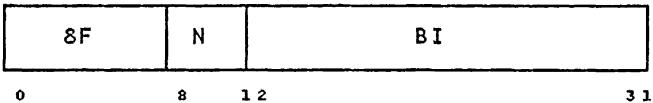

| BA           | This denotes a 24-bit absolute branch address.                                                                                                                                                                                                                                                                          |

| 0/(RC)       | This indicates the value 0 if RC is specified as 0, else the content of register RC. (i.e. if the RC field is specified as 0, a value of zero is used for the computation, if the RC field is not 0, the content of the specified register is used for the computation.) Register 0 can not be used as the RC register. |

| 0[n]         | This indicates a field of zeroes, n bits wide.                                                                                                                                                                                                                                                                          |

| //           | Two parallel bars are used to indicate a concatenation of the two fields specified on either side of the bars.                                                                                                                                                                                                          |

| (RC)         | A register specification enclosed in parentheses indicates the content of the specified register.                                                                                                                                                                                                                       |

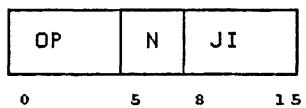

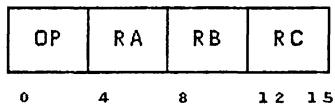

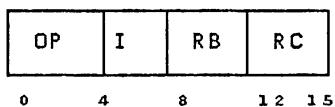

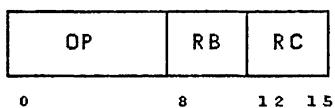

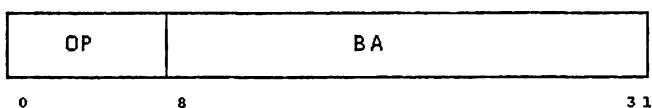

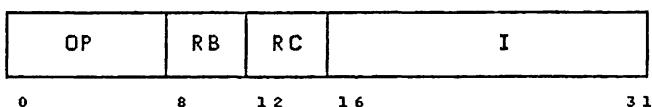

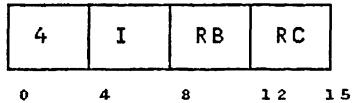

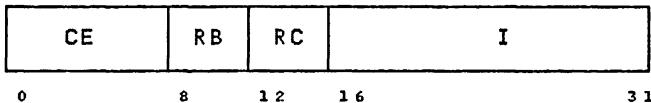

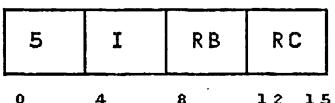

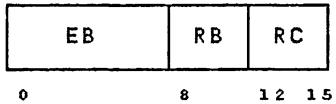

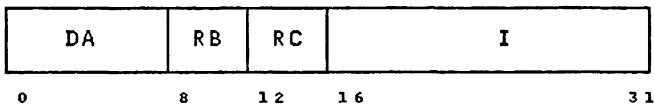

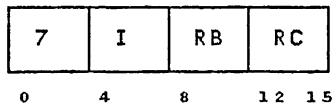

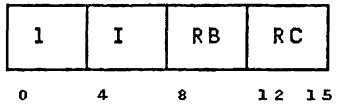

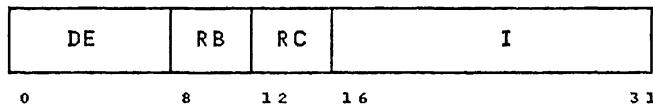

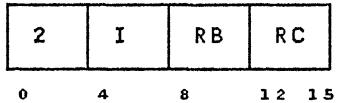

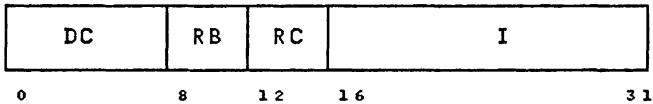

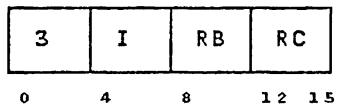

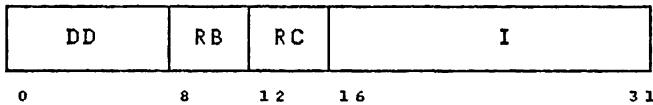

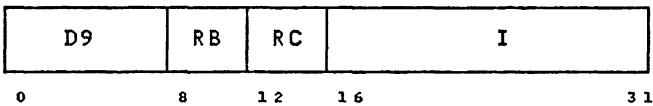

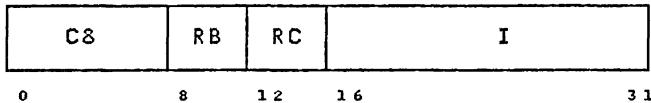

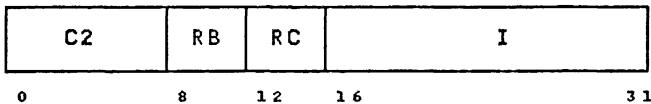

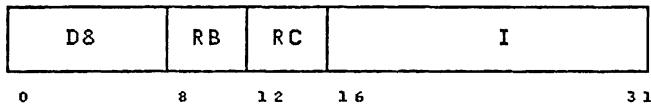

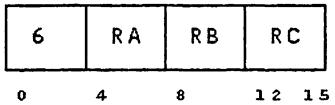

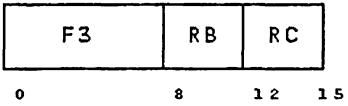

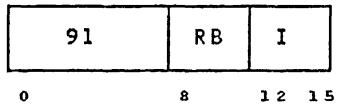

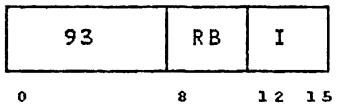

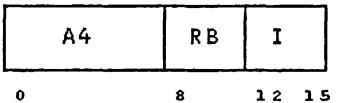

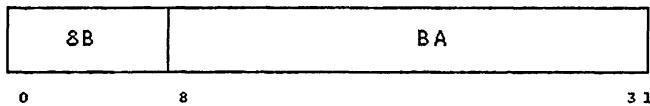

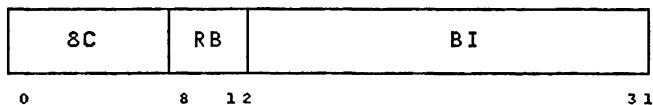

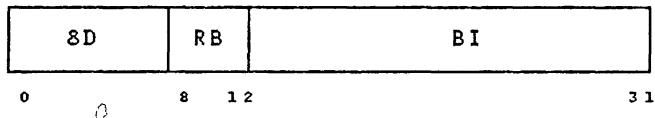

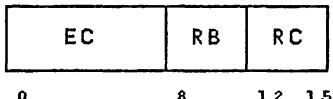

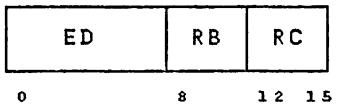

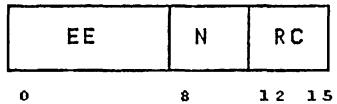

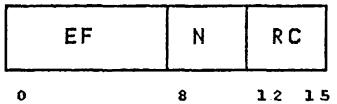

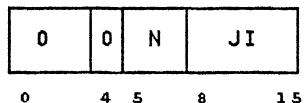

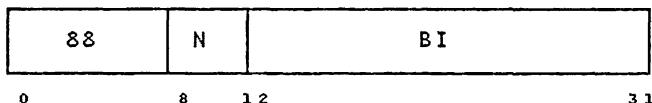

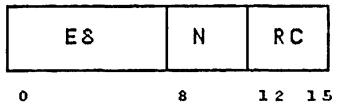

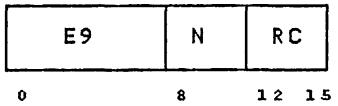

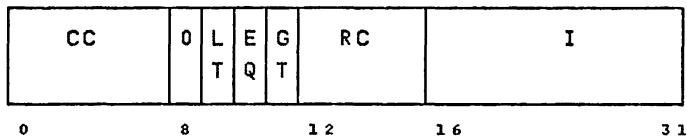

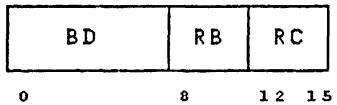

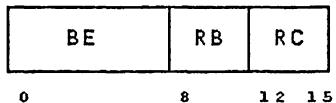

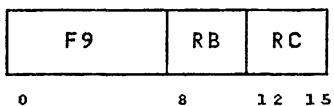

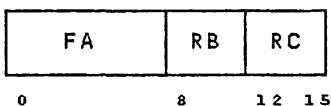

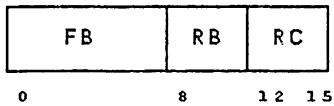

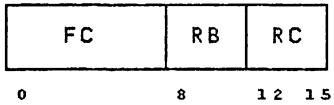

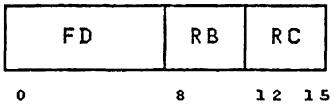

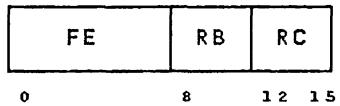

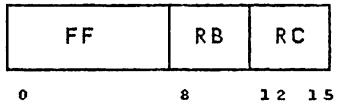

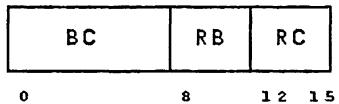

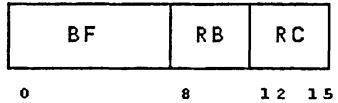

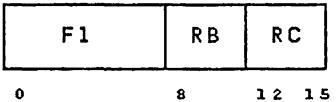

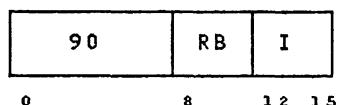

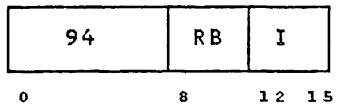

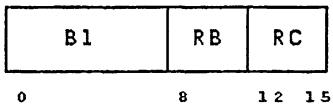

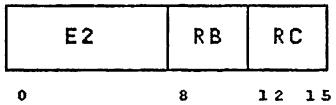

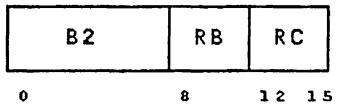

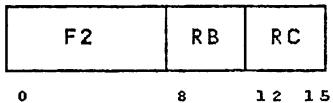

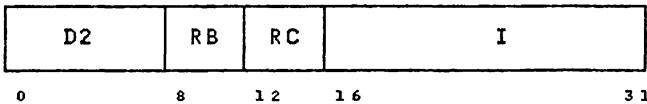

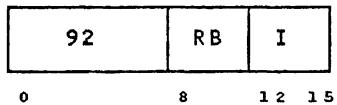

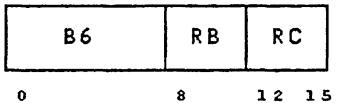

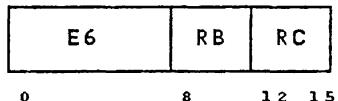

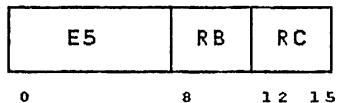

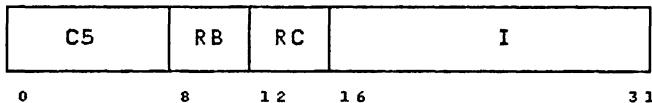

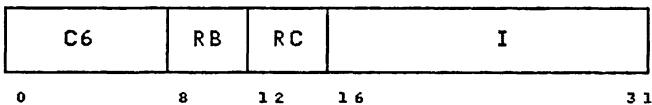

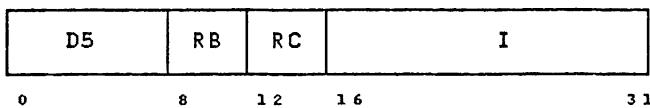

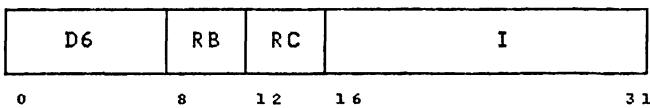

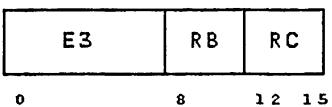

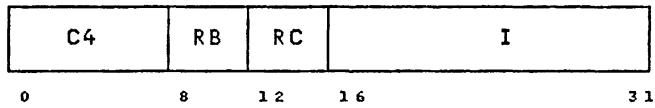

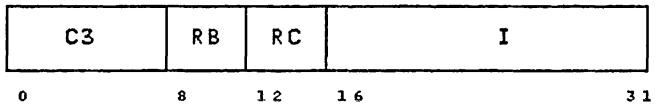

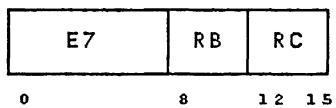

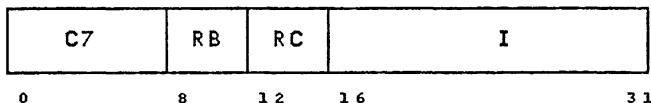

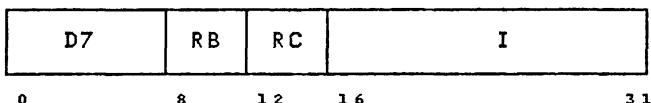

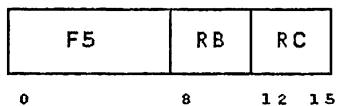

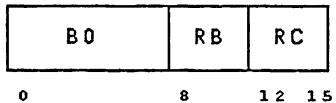

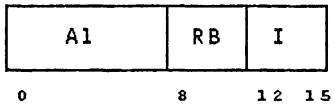

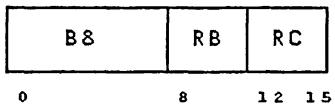

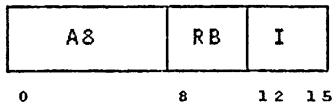

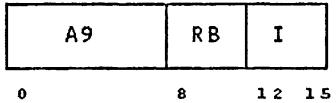

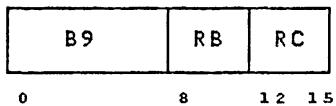

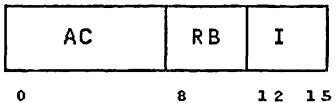

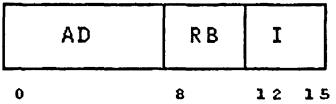

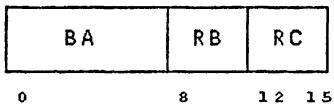

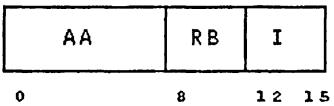

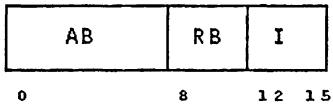

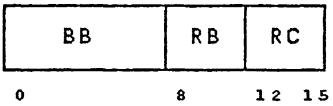

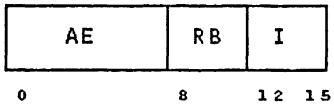

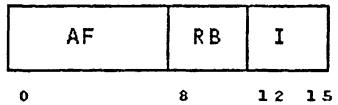

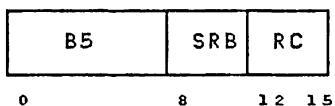

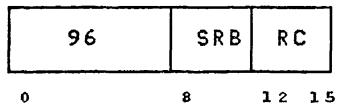

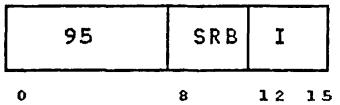

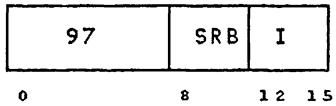

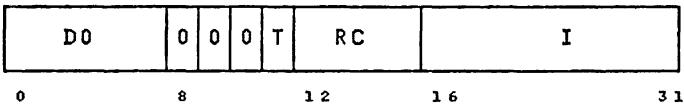

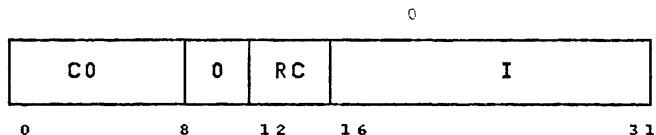

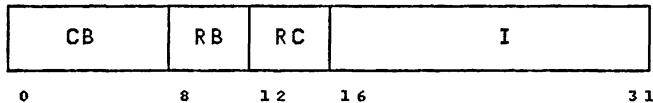

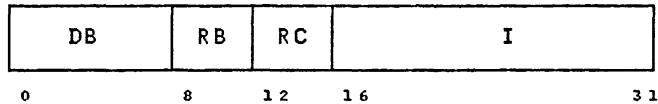

The seven instruction formats (JI, X, D-Short, R, BI, BA and D) are shown in Figure 7. Instructions are either two or four bytes in length. The first four, five or eight bits of an instruction are referred to as the operation code (op code). The JI format has a five bit op code. The X and D-Short formats both have four-bit op codes. The R, BI, BA and D formats all have eight-bit op codes. Instructions of formats JI, X, D-Short and R are all two bytes long. Instructions of formats BI, BA and D are all four bytes long.

The RA, RB and RC fields specify GPRs. The SRB field specifies an SCR. The I field specifies a displacement of a storage address or an immediate value. The N field specifies a Condition Status bit. Relative branch displacements JI and BI are both signed binary numbers in two's complement form, while BA designates an absolute branch address.

Some R format instructions have an SRB, I, or N field instead of an RB or RC field.

For X, D-Short, and D format instructions which refer to main storage or system components, the address is calculated according to the following formulas:

|                |                                   |

|----------------|-----------------------------------|

| X Format       | $(RB) + 0/(RC)$                   |

| D-Short Format | $0/(RC) + 0[28]//I$               |

|                | $0/(RC) + 0[27]//I//0[1]$         |

|                | $0/(RC) + 0[26]//I//0[2]$         |

| D Format       | $0/(RC) + 0[16]//I$               |

|                | $0/(RC) + \text{Sign Extended I}$ |

Where  $0/(RC)$  indicates the value 0 if RC is specified as 0, and the value of the content of the general purpose register if RC is specified as nonzero.

---

**JI Format**

**X Format**

**D-Short Format**

**R Format**

**BI Format**

**BA Format**

**D Format**

---

**Figure 7. Instruction Formats**

---

### 3.2 STORAGE ACCESS

Main storage is organized as a sequence of eight-bit bytes with a maximum capacity of 4,294,967,296 bytes. All storage effective addresses (base address plus displacement) are computed as 32-bit quantities. Wrap around is allowed and occurs on a 32-bit basis, i.e., main storage addressing wraps around from the architectural maximum byte address of 4,294,967,295 to address 0. This implementation of ROMP supports both 24-bit and 32-bit addressing. In 24-bit addressing mode, the high order 8 bits of the 32-bit effective address is checked to be zero. A non-zero high order byte in the effective address will result in a program check. If less than the maximum amount of main storage is installed, an attempt to utilize a byte from a non-existent main storage location will result in a program check.

All storage accesses are for a byte or multiples thereof. Instructions are provided to load or store a single character, a halfword, or a word into a general-purpose register. Storage accesses for halfwords and words ignore the low-order bit or pair of bits, respectively, of the effective address. The address of a halfword or word in main storage is the address of its leftmost byte. The Condition Status is not changed by any of these instructions.

A storage access to an invalid storage location will set the data address exception bit in the program check status and result in a program check. Refer to "Program-Check Errors" on page 124 for a description of the program check status.

All storage access instructions are non-privileged.

#### Engineering Note: Data Alignment

Data alignment for halfword and fullword accesses is normally provided in the storage controller by ignoring the low-order address bit for halfword accesses and the two low-order bits for fullword accesses. The effective storage address computed by ROMP for halfword and fullword data accesses is not aligned (i.e. the storage address is the byte address of the leftmost byte of the halfword or fullword). This allows a storage controller to support unaligned halfword and fullword accesses, if required in a particular system.

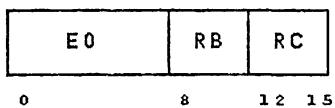

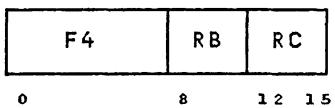

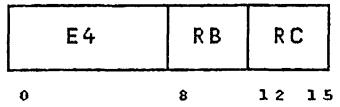

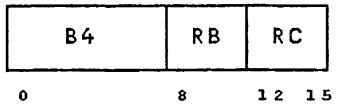

3.2.1 Load InstructionsLoad Character Short D-Short Format

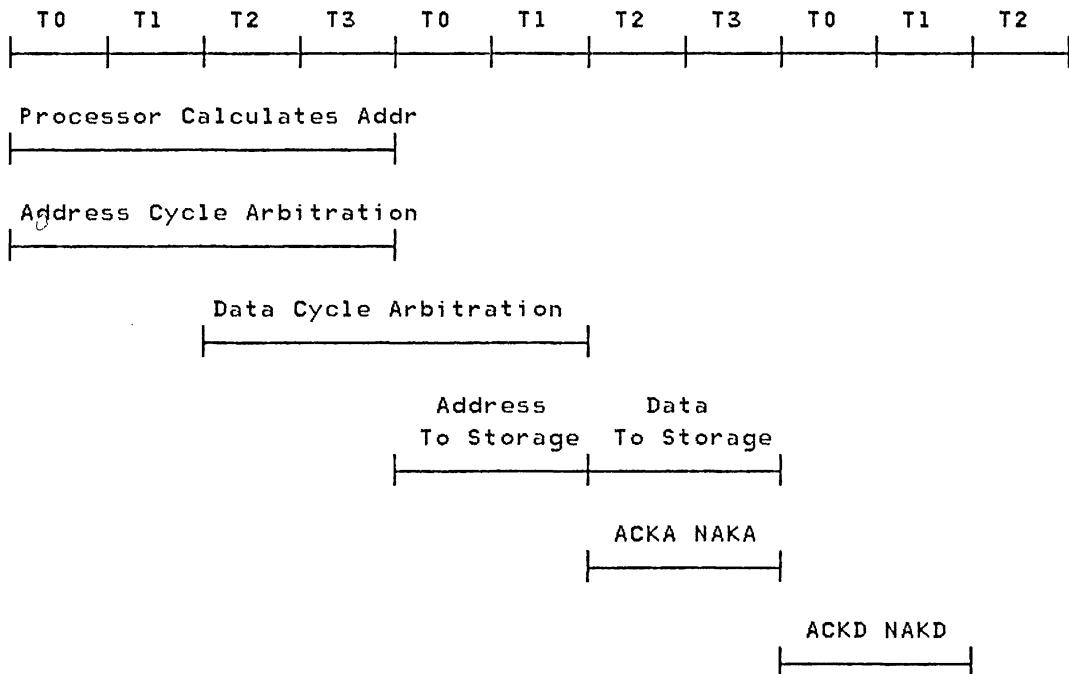

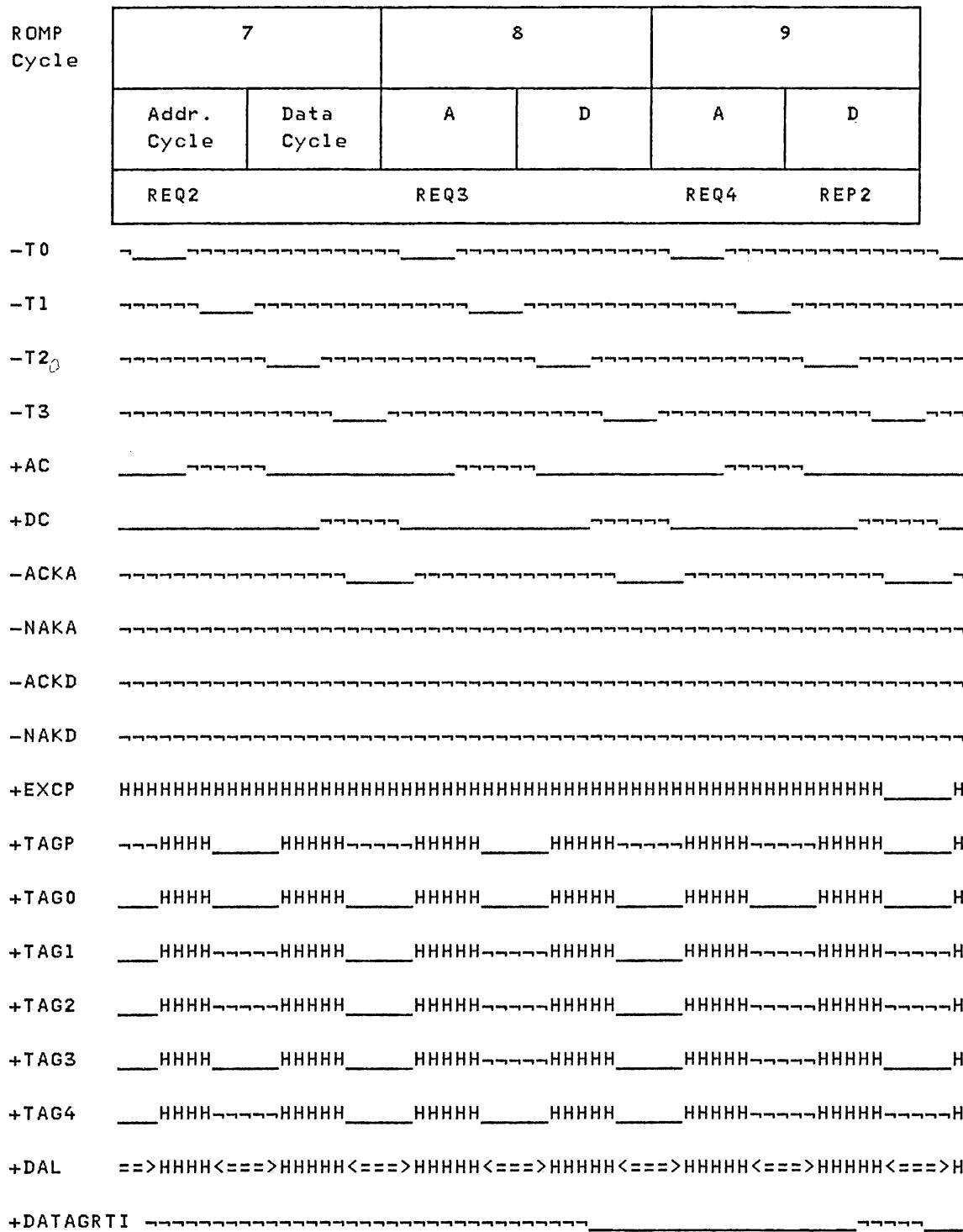

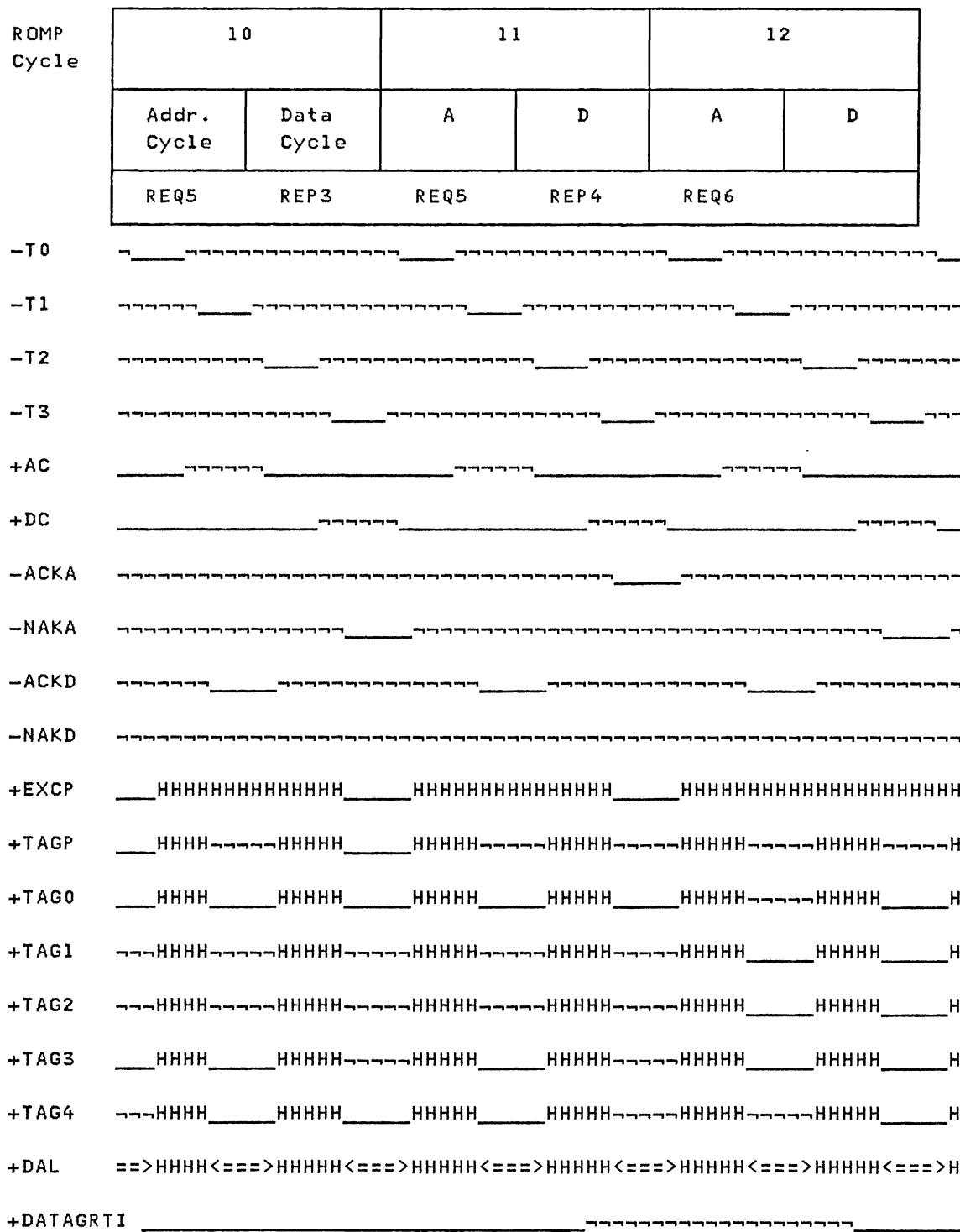

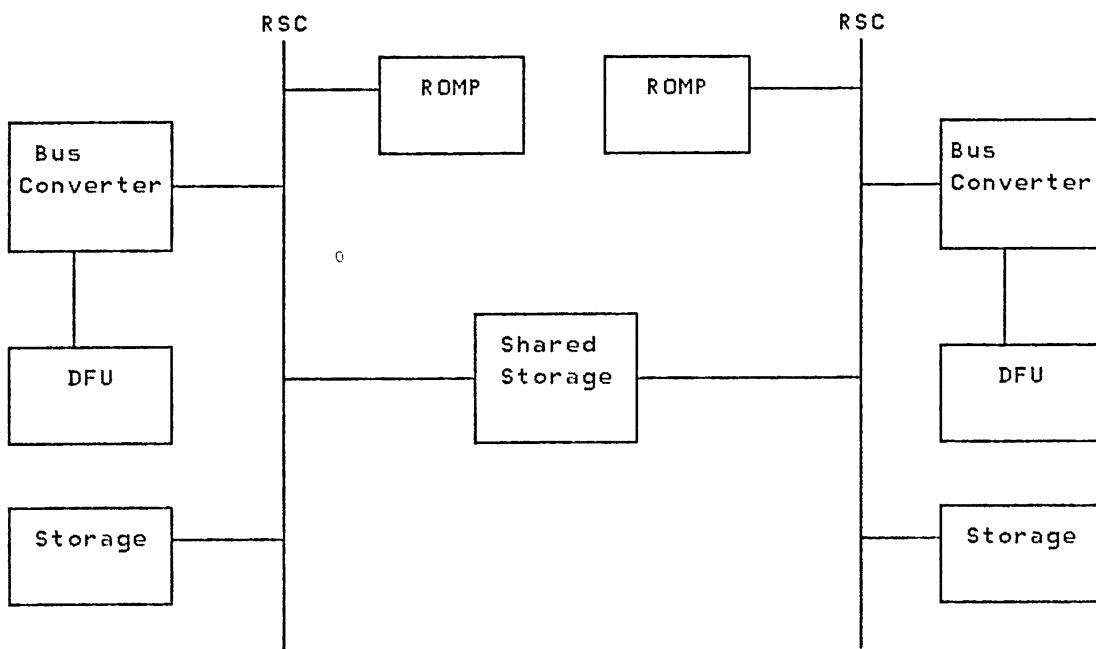

LCS RB, I(RC)